1 automatic echo mode, 2 local loopback mode, 3 remote loopback mode – Motorola ColdFire MCF5281 User Manual

Page 443

UART Modules

Freescale Semiconductor

23-23

23.4.3.1

Automatic Echo Mode

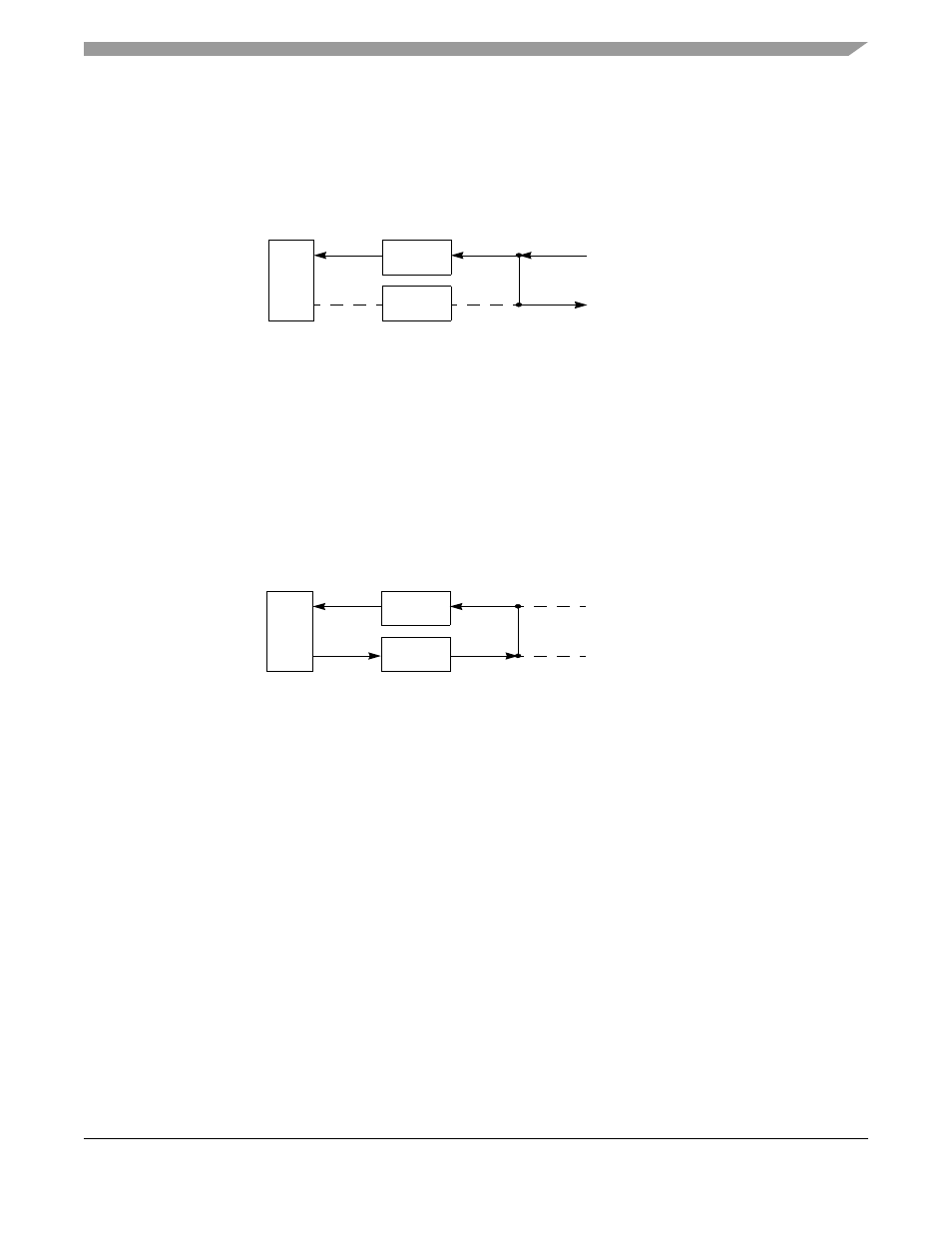

In automatic echo mode, shown in

, the UART automatically resends received data bit by bit.

The local CPU-to-receiver communication continues normally, but the CPU-to-transmitter link is

disabled. In this mode, received data is clocked on the receiver clock and re-sent on UTXDn. The receiver

must be enabled, but the transmitter need not be.

Figure 23-21. Automatic Echo

Because the transmitter is inactive, USRn[TXEMP,TXRDY] is inactive and data is sent as it is received.

Received parity is checked but not recalculated for transmission. Character framing is also checked, but

stop bits are sent as they are received. A received break is echoed as received until the next valid start bit

is detected.

23.4.3.2

Local Loopback Mode

shows how UTXDn and URXDn are internally connected in local loopback mode. This

mode is for testing the operation of a UART by sending data to the transmitter and checking data

assembled by the receiver to ensure proper operations.

Figure 23-22. Local Loopback

Features of this local loopback mode are:

•

Transmitter and CPU-to-receiver communications continue normally in this mode.

•

URXDn input data is ignored.

•

UTXDn is held marking.

•

The receiver is clocked by the transmitter clock. The transmitter must be enabled, but the receiver

need not be.

23.4.3.3

Remote Loopback Mode

In remote loopback mode, shown in

, the UART automatically transmits received data bit by

bit on the UTXDn output. The local CPU-to-transmitter link is disabled. This mode is useful in testing

receiver and transmitter operation of a remote UART. For this mode, transmitter uses the receiver clock.

Because the receiver is not active, received data cannot be read by the CPU and all status conditions are

inactive. Received parity is not checked and is not recalculated for transmission. Stop bits are sent as they

are received. A received break is echoed as received until next valid start bit is detected.

Disabled

Disabled

Tx

Rx

CPU

URXDn Input

URXDn Input

UTXDn Output

CPU

Disabled

Disabled

Tx

Rx

URXDn Input

UTXDn Output

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3