6 self-refresh operation, 6 self-refresh operation -16 – Motorola ColdFire MCF5281 User Manual

Page 288

Synchronous DRAM Controller Module

15-16

Freescale Semiconductor

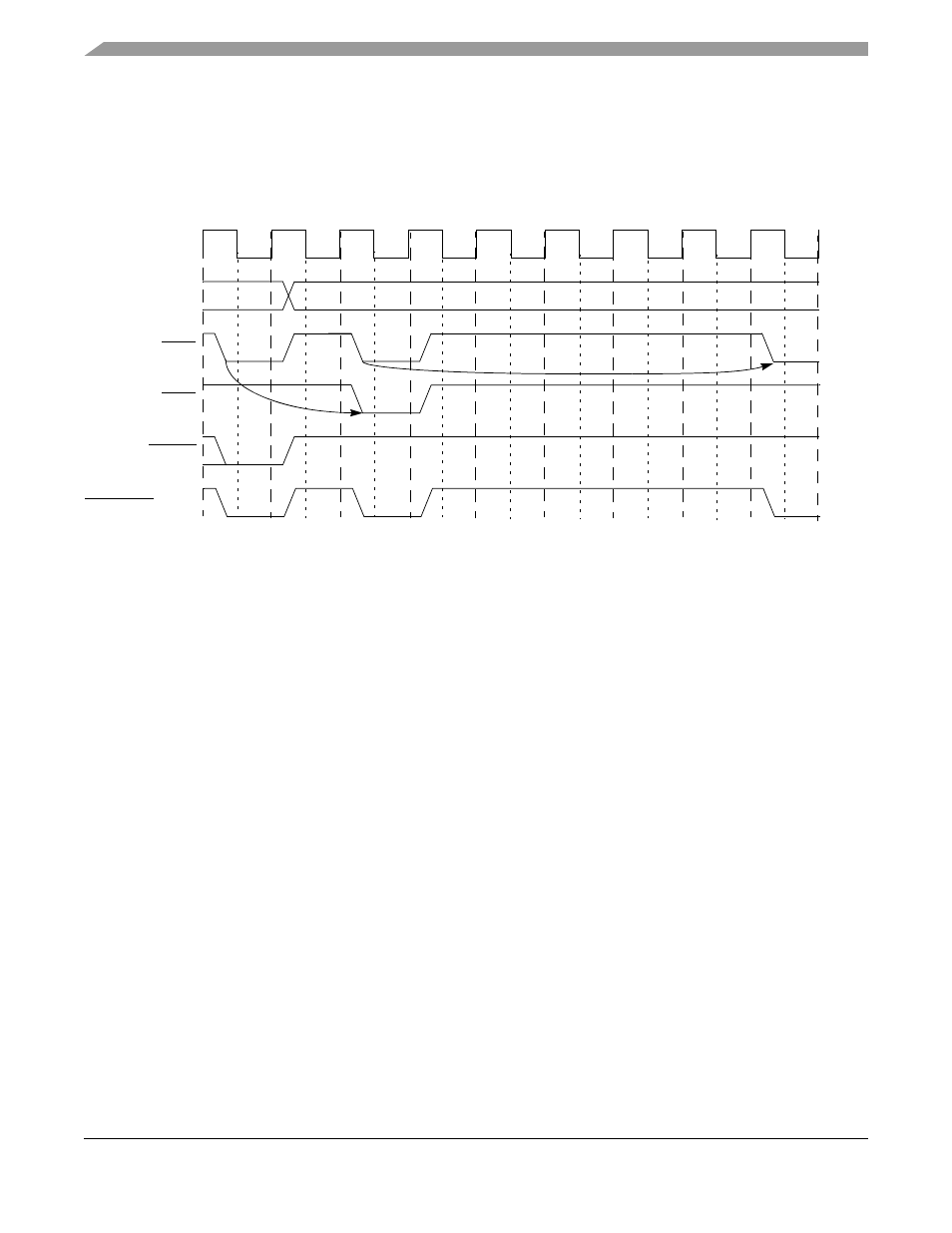

shows the auto-refresh timing. In this case, there is an SDRAM access when the refresh

request becomes active. The request is delayed by the precharge to

ACTV

delay programmed into the active

SDRAM bank by the CAS bits. The

REF

command is then generated and the delay required by

DCR[RTIM] is inserted before the next

ACTV

command is generated. In this example, the next bus cycle

is initiated, but does not generate an SDRAM access until T

RC

is finished. Because both chip selects are

active during the

REF

command, it is passed to both blocks of external SDRAM.

Figure 15-8. Auto-Refresh Operation

15.2.3.6

Self-Refresh Operation

Self-refresh is a method of allowing the SDRAM to enter into a low-power state, while at the same time

to perform an internal refresh operation and to maintain the integrity of the data stored in the SDRAM. The

DRAM controller supports self-refresh with DCR[IS]. When IS is set, the

SELF

command is sent to the

SDRAM. When IS is cleared, the

SELFX

command is sent to the DRAM controller.

shows the

self-refresh operation.

A[23:0]

SRAS

SCAS

DRAMW

PALL

SDRAM_CS[0] or [1]

REF

ACTV

t

RCD

= 2

t

RC

= 6

CLKOUT

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3