15 pulse accumulator control register (gptpactl) – Motorola ColdFire MCF5281 User Manual

Page 382

General Purpose Timer Modules (GPTA and GPTB)

20-14

Freescale Semiconductor

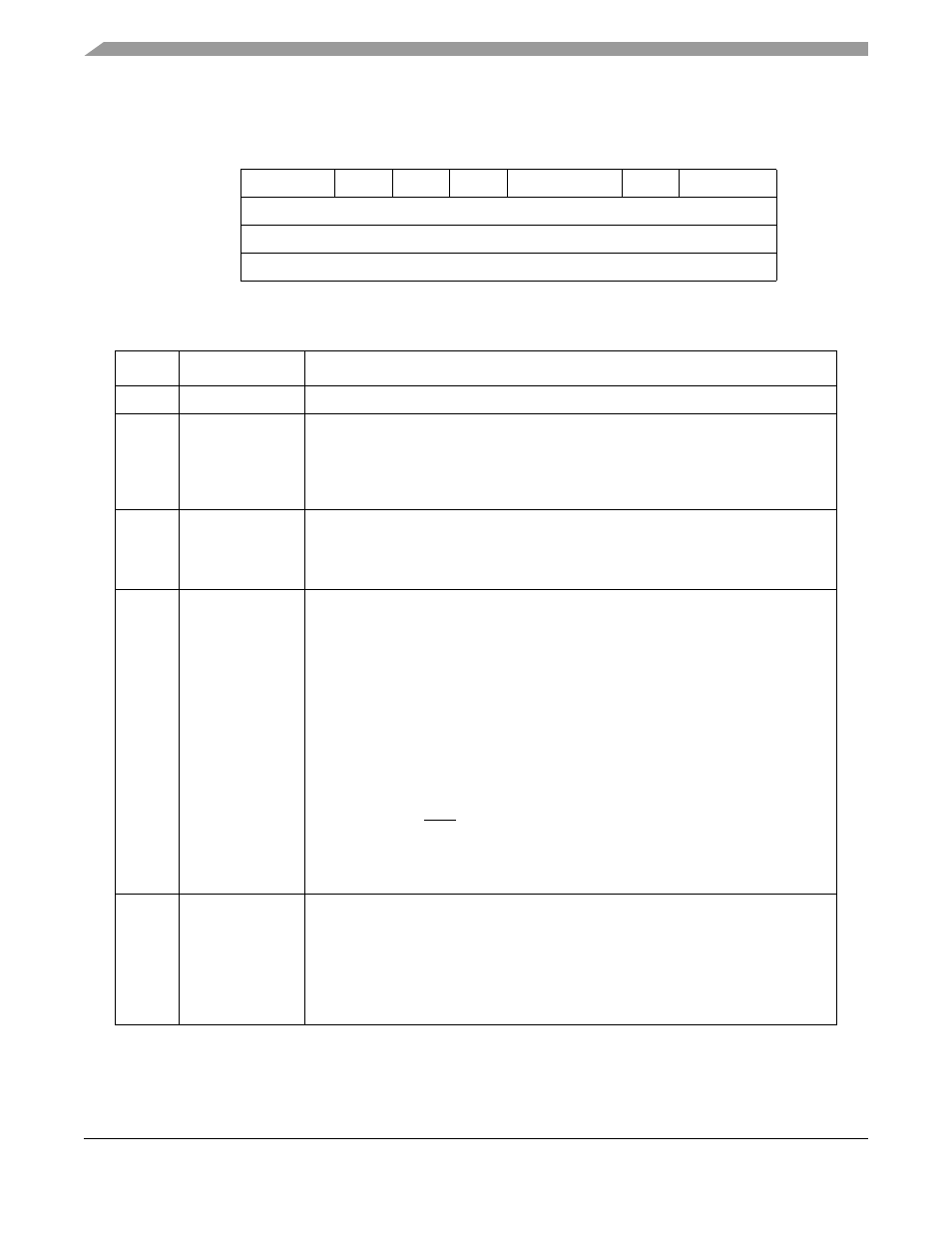

20.5.15 Pulse Accumulator Control Register (GPTPACTL)

7

6

5

4

3

0

Field

—

PAE

PAMOD PEDGE

CLK

PAOVI

PAI

Reset

0000_0000

R/W

R/W

Address

IPSBAR + 0x1A_0018, 0x1B_0018

Figure 20-17. Pulse Accumulator Control Register (GPTPACTL)

Table 20-18. GPTPACTL Field Descriptions

Bit(s)

Name

Description

7

—

Reserved, should be cleared.

6

PAE

Enables the pulse accumulator.

1 Pulse accumulator enabled

0 Pulse accumulator disabled

Note: The pulse accumulator can operate in event mode even when the GPT enable

bit, GPTEN, is clear.

5

PAMOD

Pulse accumulator mode. Selects event counter mode or gated time accumulation

mode.

1 Gated time accumulation mode

0 Event counter mode

4

PEDGE

Pulse accumulator edge. Selects falling or rising edges on the PAI pin to increment the

counter.

In event counter mode (PAMOD = 0):

1 Rising PAI edge increments counter

0 Falling PAI edge increments counter

In gated time accumulation mode (PAMOD = 1):

1 Low PAI input enables divide-by-64 clock to pulse accumulator and trailing rising

edge on PAI sets PAIF flag.

0 High PAI input enables divide-by-64 clock to pulse accumulator and trailing falling

edge on PAI sets PAIF flag.

Note: The timer prescaler generates the divide-by-64 clock. If the timer is not active,

there is no divide-by-64 clock.

To operate in gated time accumulation mode:

1. Apply logic 0 to RSTI pin.

2. Initialize registers for pulse accumulator mode test.

3. Apply appropriate level to PAI pin.

4. Enable GPT.

3–2

CLK

Select the GPT counter input clock. Changing the CLK bits causes an immediate

change in the GPT counter clock input.

00 GPT prescaler clock (When PAE = 0, the GPT prescaler clock is always the GPT

counter clock.)

01 PACLK

10 PACLK/256

11 PACLK/65536

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3