4 initialization sequence, 4 initialization sequence -17 – Motorola ColdFire MCF5281 User Manual

Page 289

Synchronous DRAM Controller Module

Freescale Semiconductor

15-17

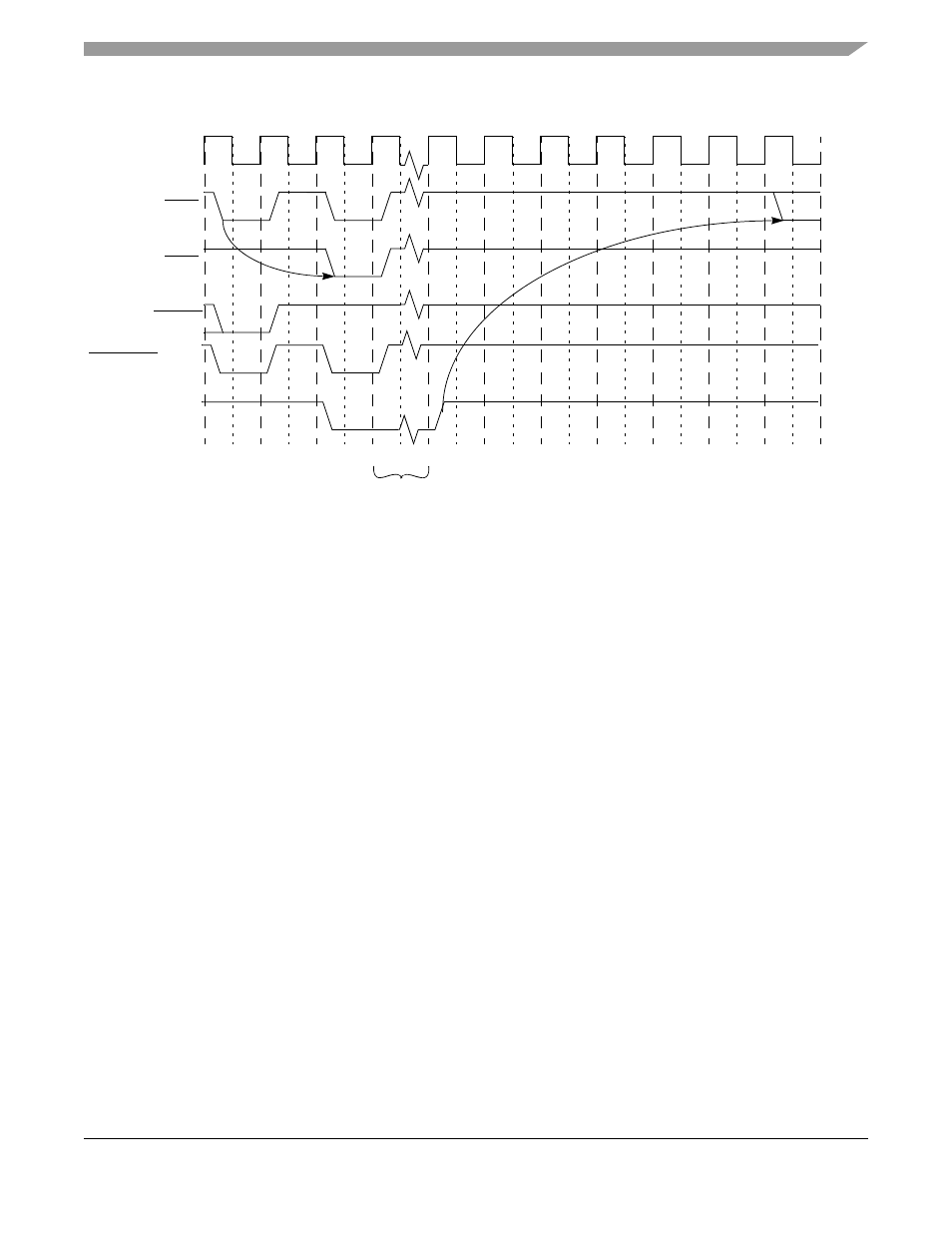

Figure 15-9. Self-Refresh Operation

15.2.4

Initialization Sequence

Synchronous DRAMs have a prescribed initialization sequence. The DRAM controller supports this

sequence with the following procedure:

1. SDRAM control signals are reset to idle state. Wait the prescribed period after reset before any

action is taken on the SDRAMs. This is normally around 100 µs.

2. Initialize the DCR, DACR, and DMR in their operational configuration. Do not yet enable

PALL

or

REF

commands.

3. Issue a

PALL

command to the SDRAMs by setting DACR[IP] and accessing a SDRAM location.

Wait the time (determined by t

RP

)

before any other execution.

4. Enable refresh (set DACR[RE]) and wait for at least 8 refreshes to occur.

5. Before issuing the

MRS

command, determine if the DMR mask bits need to be modified to allow

the

MRS

to execute properly

6. Issue the

MRS

command by setting DACR[IMRS] and accessing a location in the SDRAM. Note

that mode register settings are driven on the SDRAM address bus, so care must be taken to change

DMR[BAM] if the mode register configuration does not fall in the address range determined by

the address mask bits. After the mode register is set, DMR mask bits can be restored to their

desired configuration.

SRAS

SCAS

DRAMW

PALL

SDRAM_CS[0] or [1]

SELF

First

SCKE

Possible

ACTV

SELFX

Self-

Refresh

Active

t

RCD

= 2

t

RC

= 6

CLKOUT

(DCR[COC] = 0)

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3