4 condition code register (ccr), 4 condition code register (ccr) -6 – Motorola ColdFire MCF5281 User Manual

Page 52

ColdFire Core

2-6

Freescale Semiconductor

2.2.4

Condition Code Register (CCR)

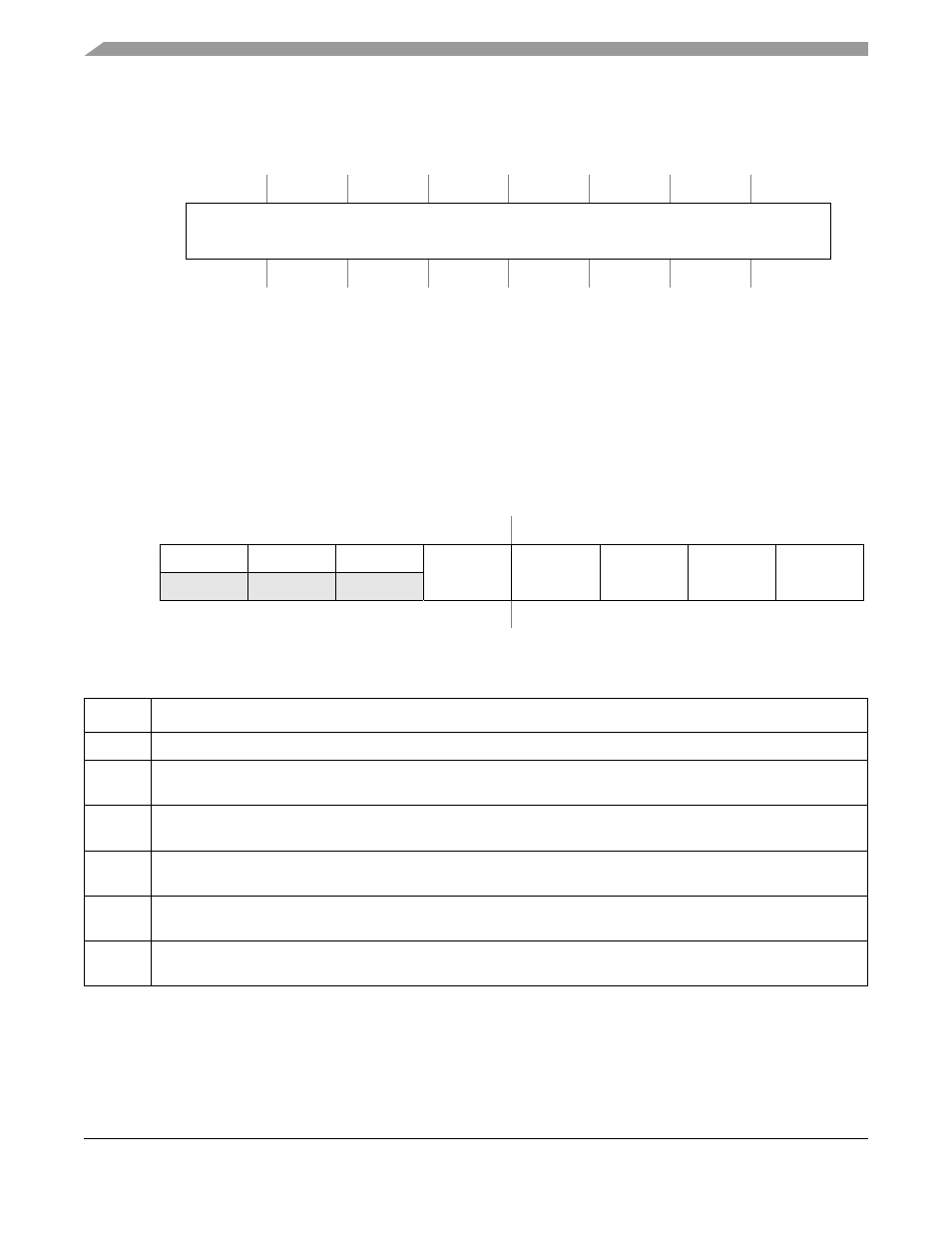

The CCR is the LSB of the processor status register (SR). Bits 4–0 act as indicator flags for results

generated by processor operations. The extend bit (X) is also an input operand during multiprecision

arithmetic computations. The CCR register must be explicitly loaded after reset and before any compare

(CMP), Bcc, or Scc instructions are executed.

BDM: Load: 0x08F (A7)

Store: 0x18F (A7)

0x800 (OTHER_A7)

Access: A7: User or BDM read/write

OTHER_A7: Supervisor or BDM read/write

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

R

Address

W

Reset – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – – –

Figure 2-4. Stack Pointer Registers (A7 and OTHER_A7)

BDM: LSB of Status Register (SR)

Access: User read/write

BDM read/write

7

6

5

4

3

2

1

0

R

0

0

0

X

N

Z

V

C

W

Reset:

0

0

0

—

—

—

—

—

Figure 2-5. Condition Code Register (CCR)

Table 2-2. CCR Field Descriptions

Field

Description

7–5

Reserved, must be cleared.

4

X

Extend condition code bit. Set to the C-bit value for arithmetic operations; otherwise not affected or set to a specified

result.

3

N

Negative condition code bit. Set if most significant bit of the result is set; otherwise cleared.

2

Z

Zero condition code bit. Set if result equals zero; otherwise cleared.

1

V

Overflow condition code bit. Set if an arithmetic overflow occurs implying the result cannot be represented in operand

size; otherwise cleared.

0

C

Carry condition code bit. Set if a carry out of the operand msb occurs for an addition or if a borrow occurs in a

subtraction; otherwise cleared.

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3