7 pll loss of lock reset, 8 loss of clock detection, 9 loss of clock reset – Motorola ColdFire MCF5281 User Manual

Page 185: 10 alternate clock selection

Clock Module

Freescale Semiconductor

9-15

9.7.4.7

PLL Loss of Lock Reset

If the LOLRE bit in the SYNCR is set, a loss of lock condition asserts reset. Reset reinitializes the LOCK

and LOCKS flags. Therefore, software must read the LOL bit in the reset status register (RSR) to

determine if a loss of lock caused the reset. See

Section 29.4.2, “Reset Status Register (RSR)

.”

To exit reset in PLL mode, the reference must be present, and the PLL must achieve lock.

In external clock mode, the PLL cannot lock. Therefore, a loss of lock condition cannot occur, and the

LOLRE bit has no effect.

9.7.4.8

Loss of Clock Detection

The LOCEN bit in the SYNCR enables the loss of clock detection circuit to monitor the input clocks to

the phase and frequency detector (PFD). When either the reference or feedback clock frequency falls

below the minimum frequency, the loss of clock circuit sets the sticky LOCS flag in the SYNSR.

NOTE

In external clock mode, the loss of clock circuit is disabled.

9.7.4.9

Loss of Clock Reset

The clock module can assert a reset when a loss of clock or loss of lock occurs. When a loss-of-clock

condition is recognized, reset is asserted if the LOCRE bit in SYNCR is set. The LOCS bit in SYNSR is

cleared after reset. Therefore, the LOC bit must be read in RSR to determine that a loss of clock condition

occurred. LOCRE has no effect in external clock mode.

To exit reset in PLL mode, the reference must be present, and the PLL must acquire lock.

Reset initializes the clock module registers to a known startup state as described in

.”

9.7.4.10

Alternate Clock Selection

Depending on which clock source fails, the loss-of-clock circuit switches the system clocks source to the

remaining operational clock. The alternate clock source generates the system clocks until reset is asserted.

As

shows, if the reference fails, the PLL goes out of lock and into self-clocked mode (SCM).

The PLL remains in SCM until the next reset. When the PLL is operating in SCM, the system frequency

depends on the value in the RFD field. The SCM system frequency stated in electrical specifications

assumes that the RFD has been programmed to binary 000. If the loss-of-clock condition is due to PLL

failure, the PLL reference becomes the system clocks source until the next reset, even if the PLL regains

and relocks.

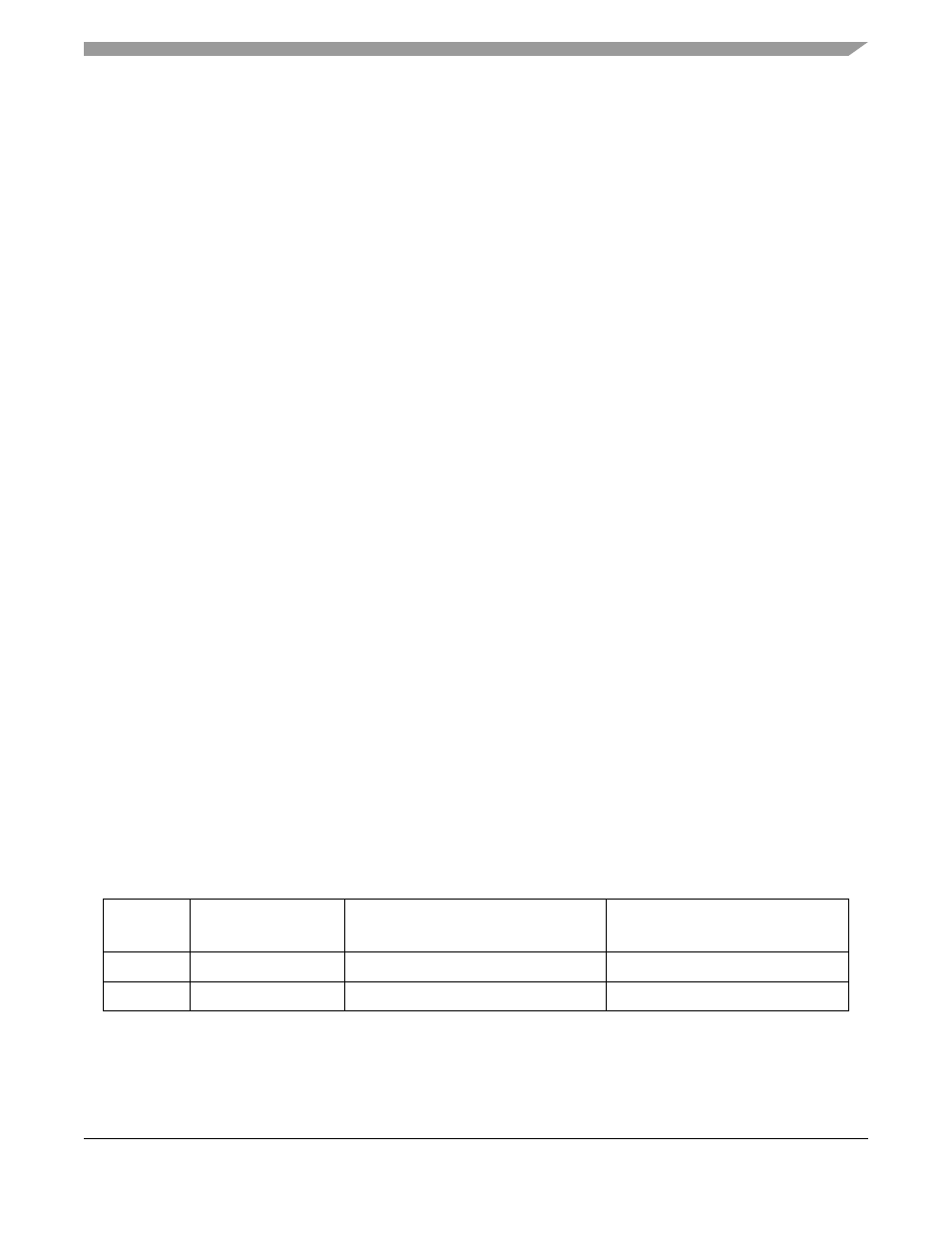

Table 9-9. Loss of Clock Summary

Clock

Mode

System Clock Source

Before Failure

Reference Failure Alternate Clock

Selected by LOC Circuit

1

Until Reset

1

The LOC circuit monitors the reference and feedback inputs to the PFD. See

PLL Failure Alternate Clock

Selected by LOC Circuit Until Reset

PLL

PLL

PLL self-clocked mode

PLL reference

External External

clock

None

NA

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3