7 clock synchronization and arbitration, 7 clock synchronization and arbitration -11 – Motorola ColdFire MCF5281 User Manual

Page 465

I

2

C Interface

Freescale Semiconductor

24-11

24.3.7

Clock Synchronization and Arbitration

I

2

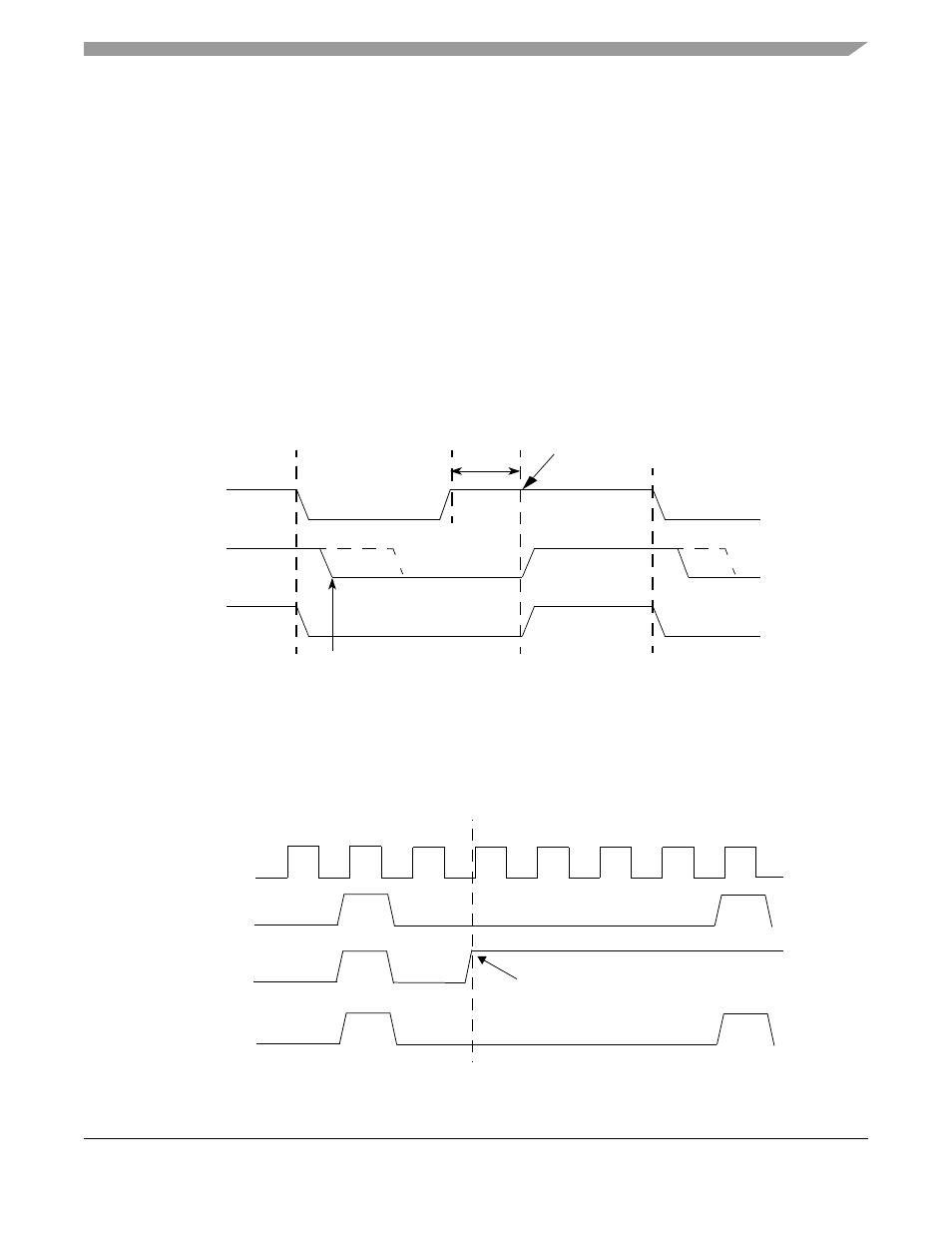

C is a true multi-master bus that allows more than one master connected to it. If two or more master

devices simultaneously request control of the bus, a clock synchronization procedure determines the bus

clock. Because wire-AND logic is performed on the I2C_SCL line, a high-to-low transition on the

I2C_SCL line affects all the devices connected on the bus. The devices start counting their low period and

after a device’s clock has gone low, it holds the I2C_SCL line low until the clock high state is reached.

However, change of low to high in this device’s clock may not change the state of the I2C_SCL line if

another device clock remains within its low period. Therefore, synchronized clock I2C_SCL is held low

by the device with the longest low period.

Devices with shorter low periods enter a high wait state during this time (see

devices concerned have counted off their low period, the synchronized clock (I2C_SCL) line is released

and pulled high. At this point, the device clocks and the I2C_SCL line are synchronized, and the devices

start counting their high periods. The first device to complete its high period pulls the I2C_SCL line low

again.

Figure 24-12. Clock Synchronization

A data arbitration procedure determines the relative priority of the contending masters. A bus master loses

arbitration if it transmits logic 1 while another master transmits logic 0. The losing masters immediately

switch over to slave receive mode and stop driving I2C_SDA output (see

transition from master to slave mode does not generate a STOP condition. Meanwhile, hardware sets

I2SR[IAL] to indicate loss of arbitration.

Figure 24-13. Arbitration Procedure

Internal Counter Reset

Wait

Start counting high period

I2C_SCL1

I2C_SCL2

I2C_SCL

Master 2 Loses Arbitration,

and becomes slave-receiver

I2C_SCL

I2C_SDA by

Master1

I2C_SDA by

Master2

I2C_SDA

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3