5 core watchdog service register (cwsr), 5 internal bus arbitration, 5 core watchdog service register (cwsr) -7 – Motorola ColdFire MCF5281 User Manual

Page 159: Internal bus arbitration -7

System Control Module (SCM)

Freescale Semiconductor

8-7

8.4.5

Core Watchdog Service Register (CWSR)

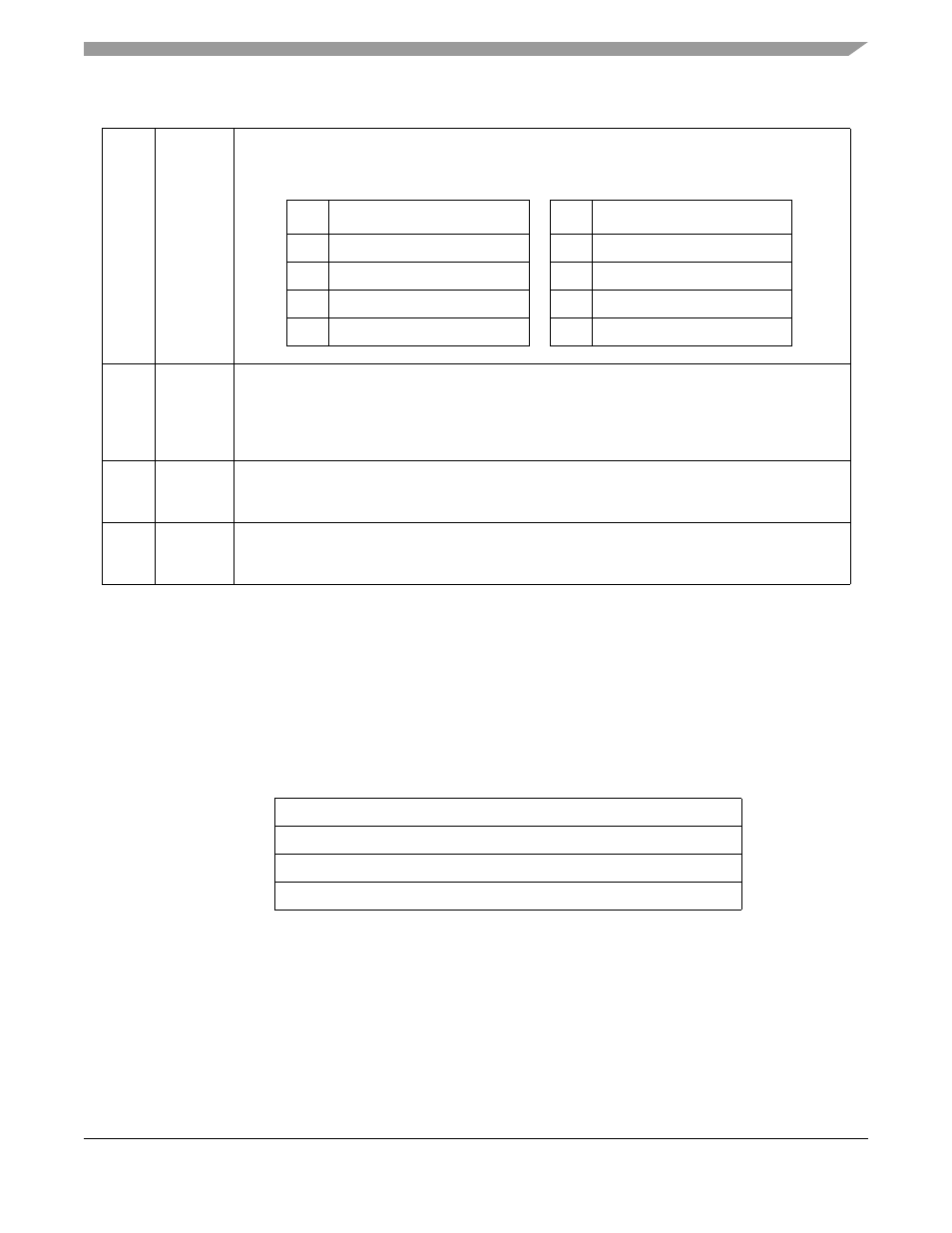

The software watchdog service sequence must be performed using the CWSR as a data register to prevent

a CWT time-out. The service sequence requires two writes to this data register: first a write of 0x55

followed by a write of 0xAA. Both writes must be performed in this order prior to the CWT time-out, but

any number of instructions or accesses to the CWSR can be executed between the two writes. If the CWT

has already timed out, writing to this register has no effect in negating the CWT interrupt.

illustrates the CWSR. At system reset, the contents of CWSR are uninitialized.

8.5

Internal Bus Arbitration

The internal bus arbitration is performed by the on-chip bus arbiter, which containing the arbitration logic

that controls which of up to four MBus masters (M0–M3 in

) has access to the external buses.

The function of the arbitration logic is described in this section.

5–3

CWT[2:0]

Core watchdog timing delay. These bits select the timeout period for the CWT. At system reset, the

CWT field is cleared signaling the minimum time-out period but the watchdog is disabled

(CWCR[CWE] = 0).

2

CWTA

Core watchdog transfer acknowledge enable.

0 CWTA Transfer acknowledge disabled.

1 CWTA Transfer Acknowledge enabled. After one CWT time-out period of the unacknowledged

assertion of the CWT interrupt, the transfer acknowledge asserts, which allows CWT to terminate

a bus cycle and allow the interrupt acknowledge to occur.

1

CWTAVAL Core watchdog transfer acknowledge valid.

0 CWTA Transfer Acknowledge has not occurred.

1 CWTA Transfer Acknowledge has occurred. Write a 1 to clear this flag bit.

0

CWTIF

Core watchdog timer interrupt flag.

0 CWT interrupt has not occurred

1 CWT interrupt has occurred. Write a 1 to clear the interrupt request.

7

0

Field

CWSR[7:0]

Reset

Uninitialized

R/W

R/W

Address

IPSBAR + 0x013

Figure 8-5. Core Watchdog Service Register (CWSR)

Table 8-5. CWCR Field Description (continued)

CWT

CWT Time-Out Period

CWT

CWT Time-Out Period

000

2

9

Bus clock frequency

100

2

19

Bus clock frequency

001

2

11

Bus clock frequency

101

2

23

Bus clock frequency

010

2

13

Bus clock frequency

110

2

27

Bus clock frequency

011

2

15

Bus clock frequency

111

2

31

Bus clock frequency

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3