6 emac instruction execution times, 6 emac instruction execution times -31 – Motorola ColdFire MCF5281 User Manual

Page 77

ColdFire Core

Freescale Semiconductor

2-31

2.3.5.6

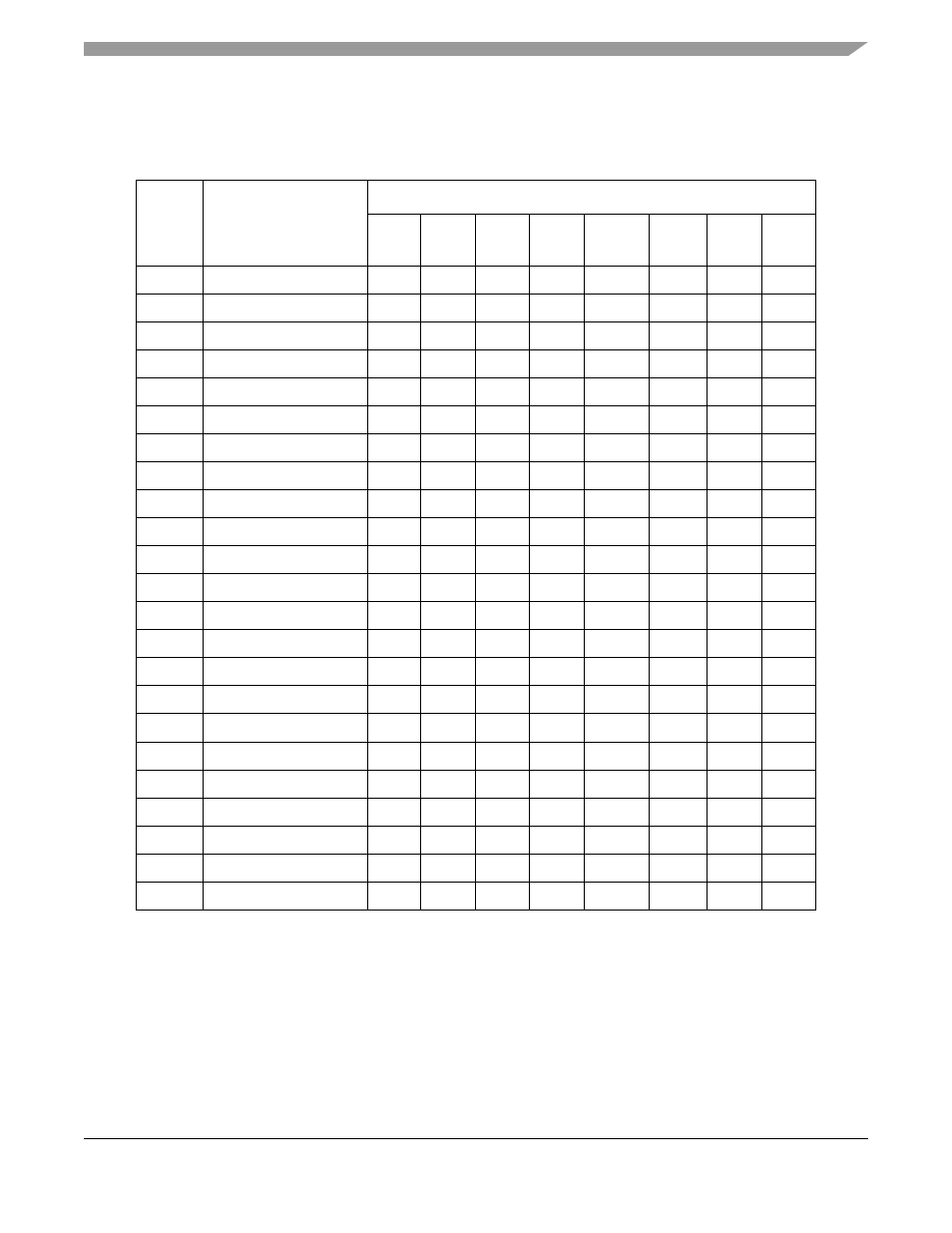

EMAC Instruction Execution Times

Table 2-17. EMAC Instruction Execution Times

Opcode

Effective Address

Rn

(An)

(An)+

-(An)

(d16,An)

(d8,An,

Xn*SF)

xxx.wl

#xxx

MAC.L

Ry, Rx, Raccx

1(0/0)

—

—

—

—

—

—

—

MAC.L

Ry, Rx,

—

(1/0)

(1/0)

(1/0)

—

—

—

MAC.W

Ry, Rx, Raccx

1(0/0)

—

—

—

—

—

—

—

MAC.W

Ry, Rx,

—

(1/0)

(1/0)

(1/0)

(1/0)

1

1

Effective address of (d16,PC) not supported

—

—

—

MOVE.L

1(0/0)

—

—

—

—

—

—

1(0/0)

MOVE.L

Raccy,Raccx

1(0/0)

—

—

—

—

—

—

—

MOVE.L

5(0/0)

—

—

—

—

—

—

5(0/0)

MOVE.L

4(0/0)

—

—

—

—

—

—

4(0/0)

MOVE.L

1(0/0)

—

—

—

—

—

—

1(0/0)

MOVE.L

1(0/0)

—

—

—

—

—

—

1(0/0)

MOVE.L

Raccx,

1(0/0)

2

2

Storing an accumulator requires one additional processor clock cycle when saturation is enabled, or fractional

rounding is performed (MACSR[7:4] equals 1---, -11-, --11)

—

—

—

—

—

—

—

MOVE.L

MACSR,

1(0/0)

—

—

—

—

—

—

—

MOVE.L

Rmask,

1(0/0)

—

—

—

—

—

—

—

MOVE.L

Raccext01, 1(0/0) — — — — — — — MOVE.L Raccext23, 1(0/0) — — — — — — — MSAC.L Ry, Rx, Raccx 1(0/0) — — — — — — — MSAC.W Ry, Rx, Raccx 1(0/0) — — — — — — — MSAC.L Ry, Rx, — (1/0) (1/0) (1/0) — — — MSAC.W Ry, Rx, — (1/0) (1/0) (1/0) — — — MULS.L 4(0/0) (1/0) (1/0) (1/0) (1/0) — — — MULS.W 4(0/0) (1/0) (1/0) (1/0) (1/0) (1/0) (1/0) 4(0/0) MULU.L 4(0/0) (1/0) (1/0) (1/0) (1/0) — — — MULU.W 4(0/0) (1/0) (1/0) (1/0) (1/0) (1/0) (1/0) 4(0/0) MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3