9 mib control register (mibc), 10 receive control register (rcr) – Motorola ColdFire MCF5281 User Manual

Page 326

Fast Ethernet Controller (FEC)

17-16

Freescale Semiconductor

The MIBC is a read/write register controlling and observing the state of the MIB block. User software

accesses this register if there is a need to disable the MIB block operation. For example, to clear all MIB

counters in RAM:

1. Disable the MIB block

2. Clear all the MIB RAM locations

3. Enable the MIB block

The MIB_DIS bit is reset to 1. See

for the locations of the MIB counters.

17.4.10 Receive Control Register (RCR)

RCR controls the operational mode of the receive block and must be written only when ECR[ETHER_EN]

is cleared (initialization time).

50 MHz

0xA

2.50 MHz

66 MHz

0xE

2.36 MHz

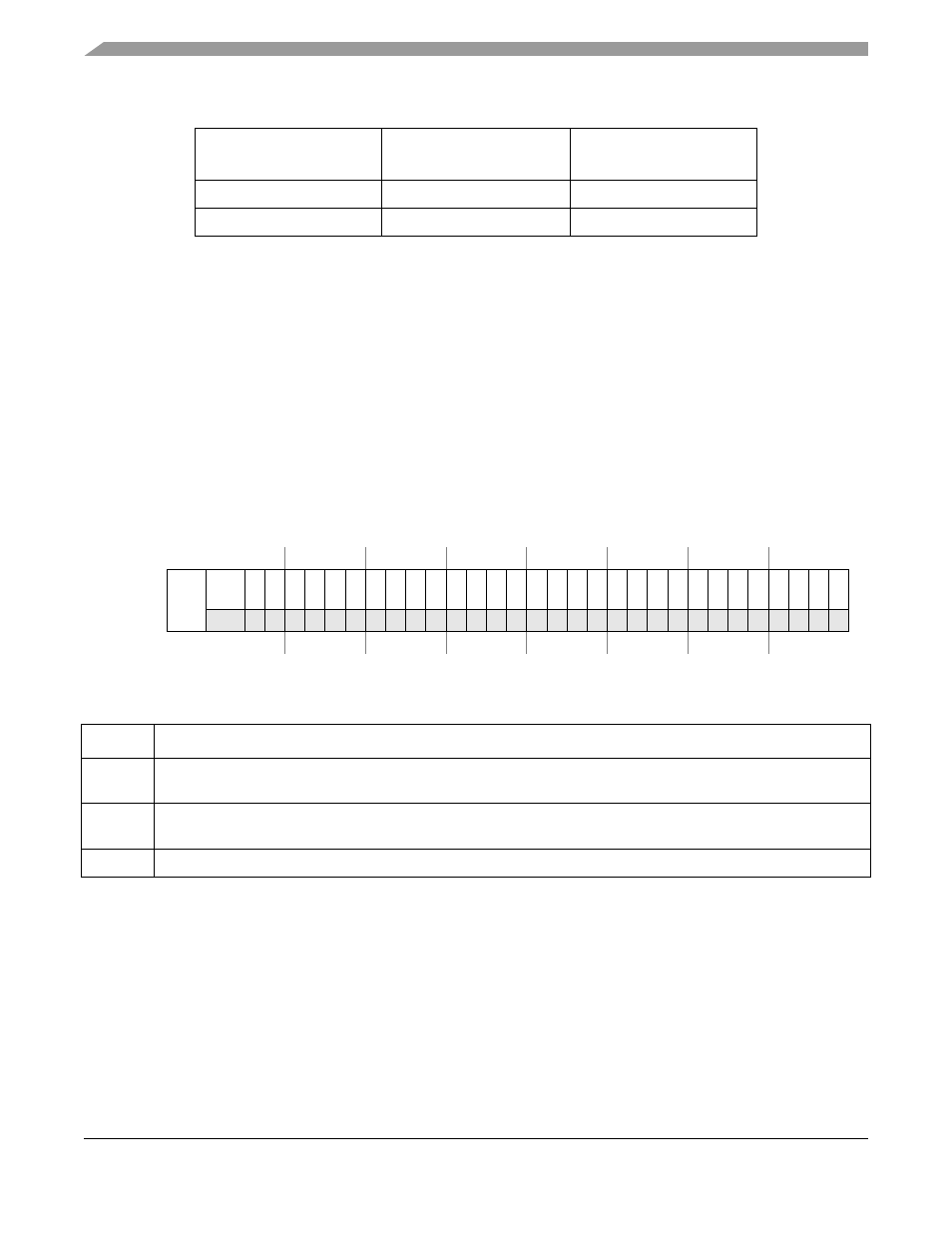

IPSBAR

Offset:

0x1064

Access: User read/write

31

30

29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

R

MIB_

DIS

MIB_

IDLE

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

W

Reset

1

1

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Figure 17-9. MIB Control Register (MIBC)

Table 17-13. MIBC Field Descriptions

Field

Description

31

MIB_DIS

A read/write control bit. If set, the MIB logic halts and not update any MIB counters.

30

MIB_IDLE

A read-only status bit. If set the MIB block is not currently updating any MIB counters.

29–0

Reserved.

Table 17-12. Programming Examples for MSCR (continued)

Internal FEC Clock

Frequency

MSCR[MII_SPEED]

FEC_MDC frequency

17.4.9

MIB Control Register (MIBC)

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3