4 dma timer reference registers (dtrrn), 5 dma timer capture registers (dtcrn), 4 dma timer reference registers (dtrr – Motorola ColdFire MCF5281 User Manual

Page 399: 5 dma timer capture registers (dtcr, 4 dma timer reference registers (dtrr n ), 5 dma timer capture registers (dtcr n )

DMA Timers (DTIM0–DTIM3)

Freescale Semiconductor

21-7

21.2.4

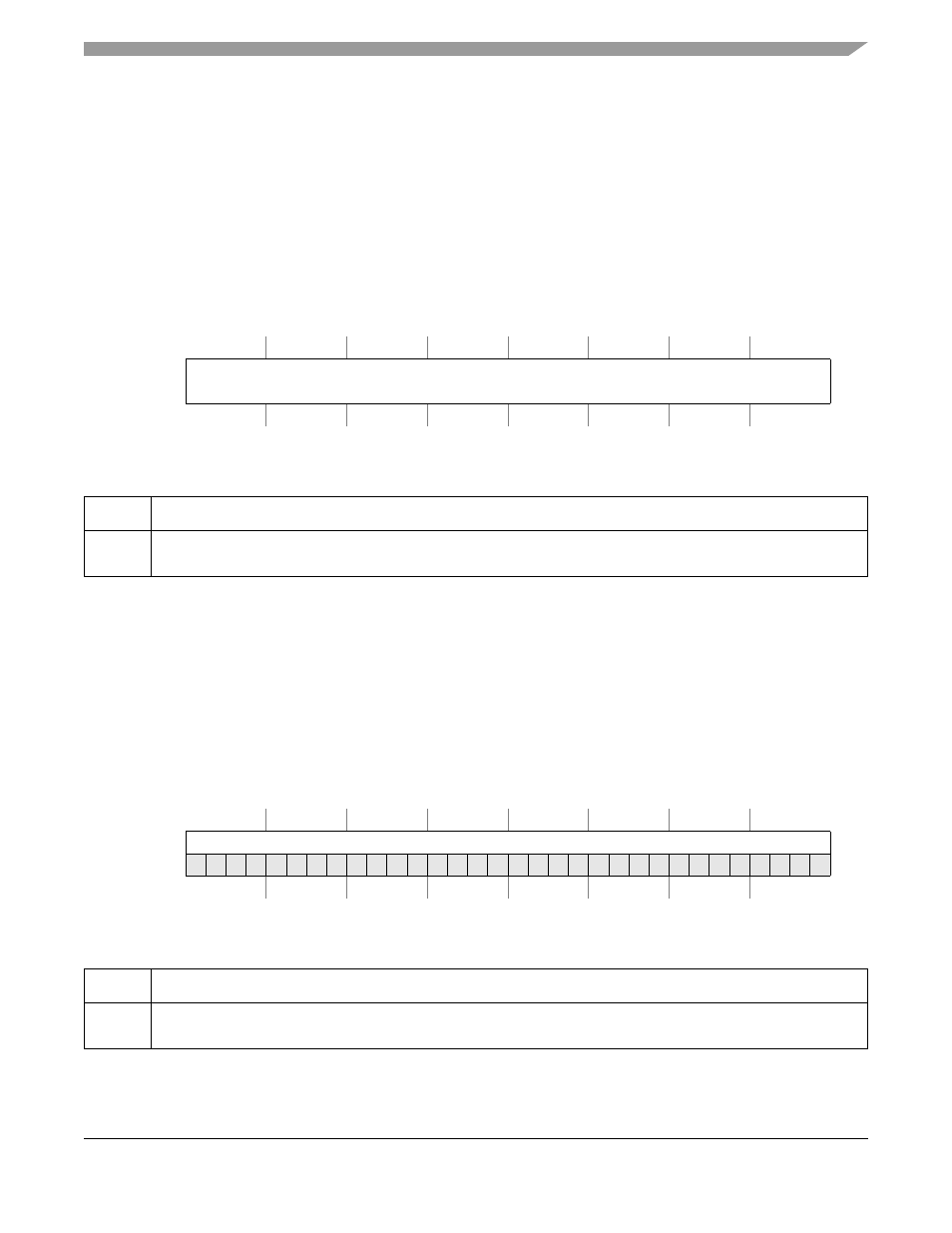

DMA Timer Reference Registers (DTRRn)

As part of the output-compare function, each DTRRn contains the reference value compared with the

respective free-running timer counter (DTCNn).

The reference value is matched when DTCNn equals DTRRn. The prescaler indicates that DTCNn should

be incremented again. Therefore, the reference register is matched after DTRRn + 1 time intervals.

21.2.5

DMA Timer Capture Registers (DTCRn)

Each DTCRn latches the corresponding DTCNn value during a capture operation when an edge occurs on

DTINn, as programmed in DTMRn. The internal bus clock is assumed to be the clock source. DTINn

cannot simultaneously function as a clocking source and as an input capture pin. Indeterminate operation

results if DTINn is set as the clock source when the input capture mode is used.

IPSBAR

Offset:

0x00_0404 (DTRR0)

0x00_0444 (DTRR1)

0x00_0484 (DTRR2)

0x00_04C4 (DTRR3)

Access: User read/write

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

R

REF (32-bit reference value)

W

Reset 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

Figure 21-5. DTRRn Registers

Table 21-5. DTRRn Field Descriptions

Field

Description

31–0

REF

Reference value compared with the respective free-running timer counter (DTCNn) as part of the output-compare

function.

IPSBAR

Offset:

0x00_0408

(

DTCR0

)

0x00_0448

(

DTCR1

)

0x00_0488

(

DTCR2

)

0x00_04C8

(

DTCR3

)

Access: User read-only

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

R

CAP (32-bit capture counter value)

W

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Figure 21-6. DTCRn Registers

Table 21-6. DTCRn Field Descriptions

Field

Description

31–0

CAP

Captures the corresponding DTCNn value during a capture operation when an edge occurs on DTIN

n

, as

programmed in DTMRn.

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3