13 physical address upper register (paur), 14 opcode/pause duration register (opd) – Motorola ColdFire MCF5281 User Manual

Page 329

Fast Ethernet Controller (FEC)

Freescale Semiconductor

17-19

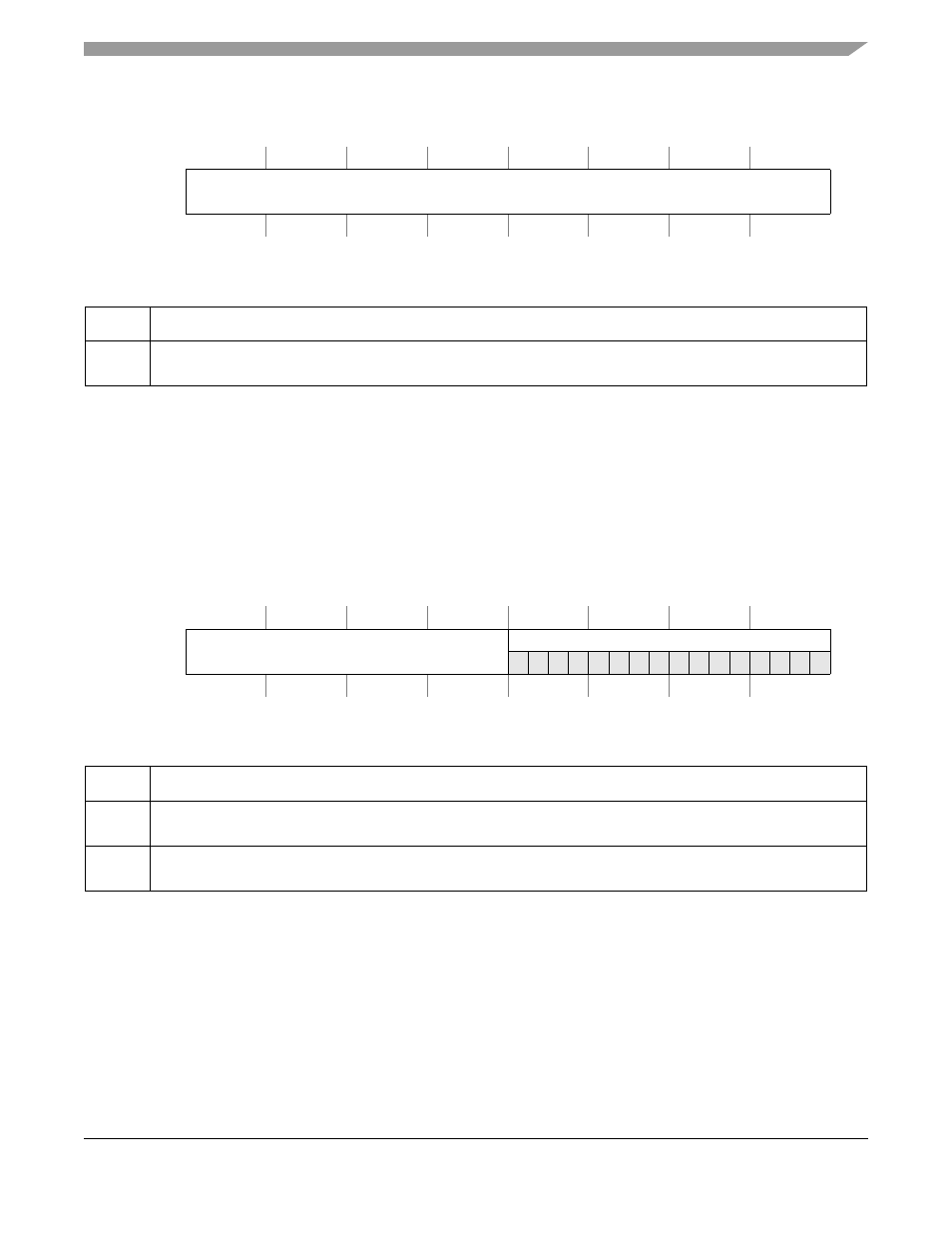

17.4.13 Physical Address Upper Register (PAUR)

PAUR contains the upper 16 bits (bytes 4 and 5) of the 48-bit address used in the address recognition

process to compare with the DA (destination address) field of receive frames with an individual DA. In

addition, this register is used in bytes 4 and 5 of the 6-byte Source Address field when transmitting PAUSE

frames. Bits 15:0 of PAUR contain a constant type field (0x8808) for transmission of PAUSE frames. The

upper 16 bits of this register are not reset and you must initialize it.

17.4.14 Opcode/Pause Duration Register (OPD)

The OPD is read/write accessible. This register contains the 16-bit opcode and 16-bit pause duration fields

used in transmission of a PAUSE frame. The opcode field is a constant value, 0x0001. When another node

detects a PAUSE frame, that node pauses transmission for the duration specified in the pause duration

field. The lower 16 bits of this register are not reset and you must initialize them.

IPSBAR

Offset:

0x10E4

Access: User read/write

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

R

PADDR1

W

Reset — — — — — — — — — — — — — — — — — — — — — — — — — — — — — — — —

Figure 17-12. Physical Address Lower Register (PALR)

Table 17-16. PALR Field Descriptions

Field

Description

31–0

PADDR1

Bytes 0 (bits 31:24), 1 (bits 23:16), 2 (bits 15:8), and 3 (bits 7:0) of the 6-byte individual address are used for exact

match and the source address field in PAUSE frames.

IPSBAR

Offset:

0x10E8

Access: User read/write

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

R

PADDR2

TYPE

W

Reset — — — — — — — — — — — — — — — — 1 0 0 0 1 0 0 0 0 0 0 0 1 0 0 0

Figure 17-13. Physical Address Upper Register (PAUR)

Table 17-17. PAUR Field Descriptions

Field

Description

31–16

PADDR2

Bytes 4 (bits 31:24) and 5 (bits 23:16) of the 6-byte individual address used for exact match, and the source address

field in PAUSE frames.

15–0

TYPE

Type field in PAUSE frames. These 16 read-only bits are a constant value of 0x8808.

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3