Motorola ColdFire MCF5281 User Manual

Page 624

Debug Support

30-6

Freescale Semiconductor

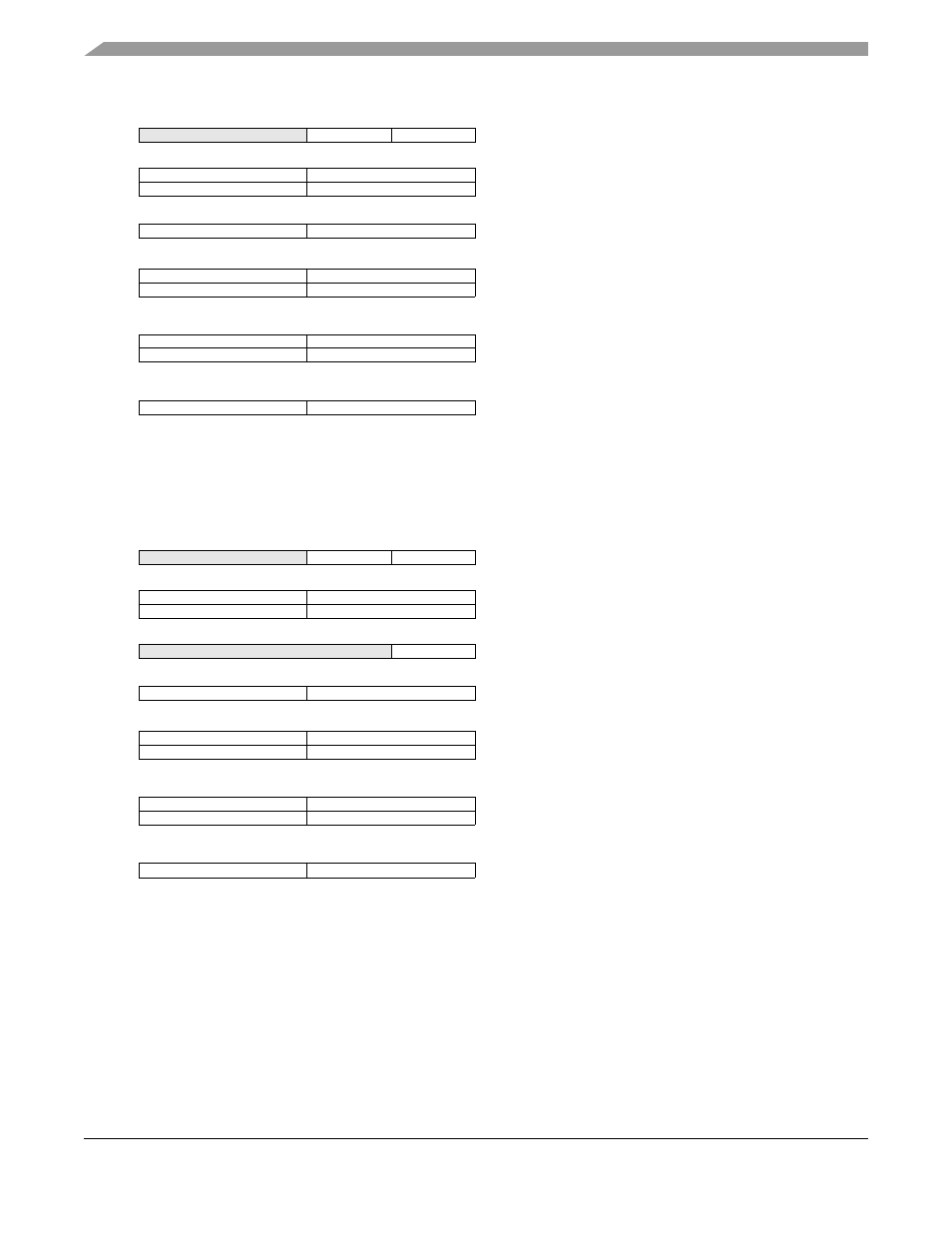

Figure 30-4. Debug Programming Model

These registers are accessed through the BDM port by the commands,

WDMREG

and

RDMREG

, described

in

Section 30.5.3.3, “Command Set Descriptions

.” These commands contain a 5-bit field, DRc, that

specifies the register, as shown in

PC breakpoint mask register

PC breakpoint register

Data breakpoint register

Data breakpoint mask register

Trigger definition register

Configuration/status register

Note: Each debug register is accessed as a 32-bit register; shaded fields above are not used (don’t care).

All debug control registers are writable from the external development system or the CPU via the WDEBUG

instruction. CSR is write-only from the programming model. It can be read or written through the BDM port

using the

RDMREG

and

WDMREG

commands

.

Address attribute trigger register

Address low breakpoint register

Address high breakpoint register

31

15

7

0

31

15

0

31

15

0

31

15

0

31

15

0

31

15

0

AATR

ABLR

ABHR

CSR

DBR

DBMR

PBR

PBMR

TDR

PC breakpoint mask register

PC breakpoint register

Data breakpoint register

Data breakpoint mask register

Trigger definition register

Configuration/status register

BDM address attribute register

Note: Each debug register is accessed as a 32-bit register; shaded fields above are not used (don’t care).

All debug control registers are writable from the external development system or the CPU via the WDEBUG

instruction.

CSR is write-only from the programming model. It can be read or written through the BDM port using the

RDMREG

and

WDMREG

commands

.

Address attribute trigger register

Address low breakpoint register

Address high breakpoint register

31

15

7

0

31

15

7

0

31

15

0

31

15

0

31

15

0

31

15

0

31

15

0

31

15

0

AATR

ABLR

ABHR

BAAR

CSR

DBR

DBMR

PBR

PBMR

TDR

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3