Motorola ColdFire MCF5281 User Manual

Page 739

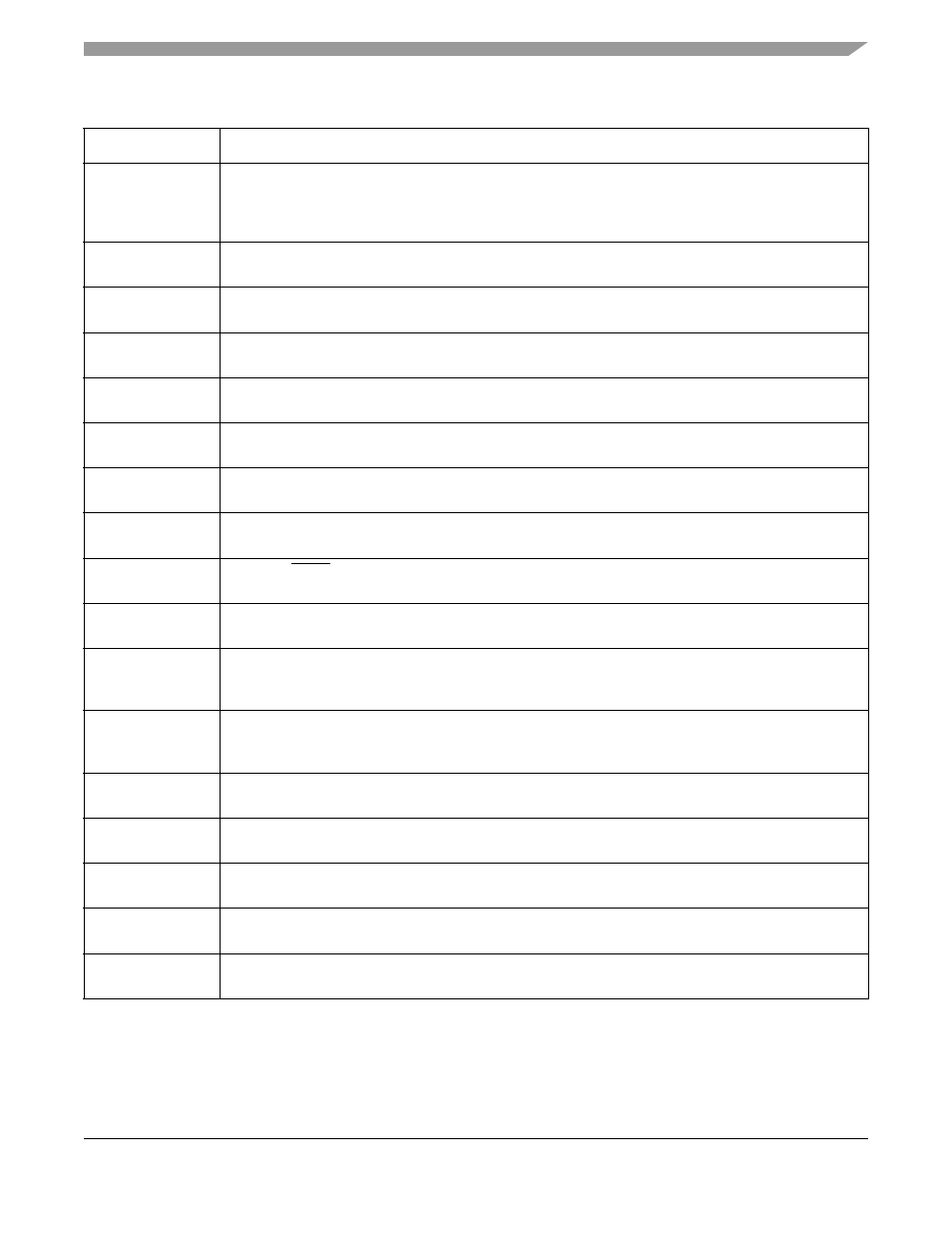

Revision History

Freescale Semiconductor

B-3

Moved information in Section 8.4.6, “DMA Request Control Register,” to

.”

Changed offset for the copy of RAMBAR to “0x008.”

Changed CWTIC to CWTIF.

Changed text to read “Setting MPARK[PRK_LAST] causes the arbitration pointer to be parked on the

highest priority master.”

Changed “

÷

MFD (2–9)” to “

÷

MFD (4–18).”

Changed equation in “Normal PLL Clock Mode” row to the following:

f

sys

= f

ref

×

2(MFD + 2)/2

RFD

Eliminated Section 12.4.1.4, “Code Example.”

In “Reset: CSCR0” row, changed “D7, D6, D5” to “—, D19, D18.”

Replaced “SCKE” with “SCKE.”

Changed text to read “The transmit FIFO uses addresses from the start of the FIFO to the location four

bytes before the address programmed into the FRSR.”

Added the following footnote: “The receive buffer pointer, which contains the address of the associated

data buffer, must always be evenly divisible by 16. The buffer must reside in memory external to the FEC.

This value is never modified by the Ethernet controller.”

Added the following footnote: “The transmit buffer pointer, which contains the address of the associated

data buffer, must always be evenly divisible by 4. The buffer must reside in memory external to the FEC.

This value is never modified by the Ethernet controller.”

Changed value in “Divide by” block to 8192.

Multiplied all system clock divisor values in PRE field description by 2.

Changed equation in text to the following:

Timeout period = PRE[3:0]

× (

PM[15:0] + 1)

×

system clock

÷

2

In “UISR Field” row, changed bit 6 to a reserved bit.

Changed bit 6 to a reserved bit.

Table B-2. Rev. 0.1 to Rev. 1 Changes (continued)

Location

Description

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3