1 dma module features, 2 dma request control (dmareqc), 1 dma module features -2 – Motorola ColdFire MCF5281 User Manual

Page 298: 2 dma request control (dmareqc) -2

DMA Controller Module

16-2

Freescale Semiconductor

NOTE

Throughout this chapter “external request” and DREQ are used to refer to a

DMA request from one of the on-chip UARTS or DMA timers. For details

on the connections associated with DMA request inputs, see

“DMA Request Control (DMAREQC)

16.1.1

DMA Module Features

The DMA controller module features are as follows:

•

Four independently programmable DMA controller channels

•

Auto-alignment feature for source or destination accesses

•

Dual-address transfers

•

Channel arbitration on transfer boundaries

•

Data transfers in 8-, 16-, 32-, or 128-bit blocks using a 16-byte buffer

•

Continuous-mode or cycle-steal transfers

•

Independent transfer widths for source and destination

•

Independent source and destination address registers

16.2

DMA Request Control (DMAREQC)

The DMAREQC register provides a software-controlled connection matrix for DMA requests. It logically

routes DMA requests from the DMA timers and UARTs to the four channels of the DMA controller.

Writing to this register determines the exact routing of the DMA request to the four channels of the DMA

modules. If DCRn[EEXT] is set and the channel is idle, the assertion of the appropriate DREQn activates

channel n.

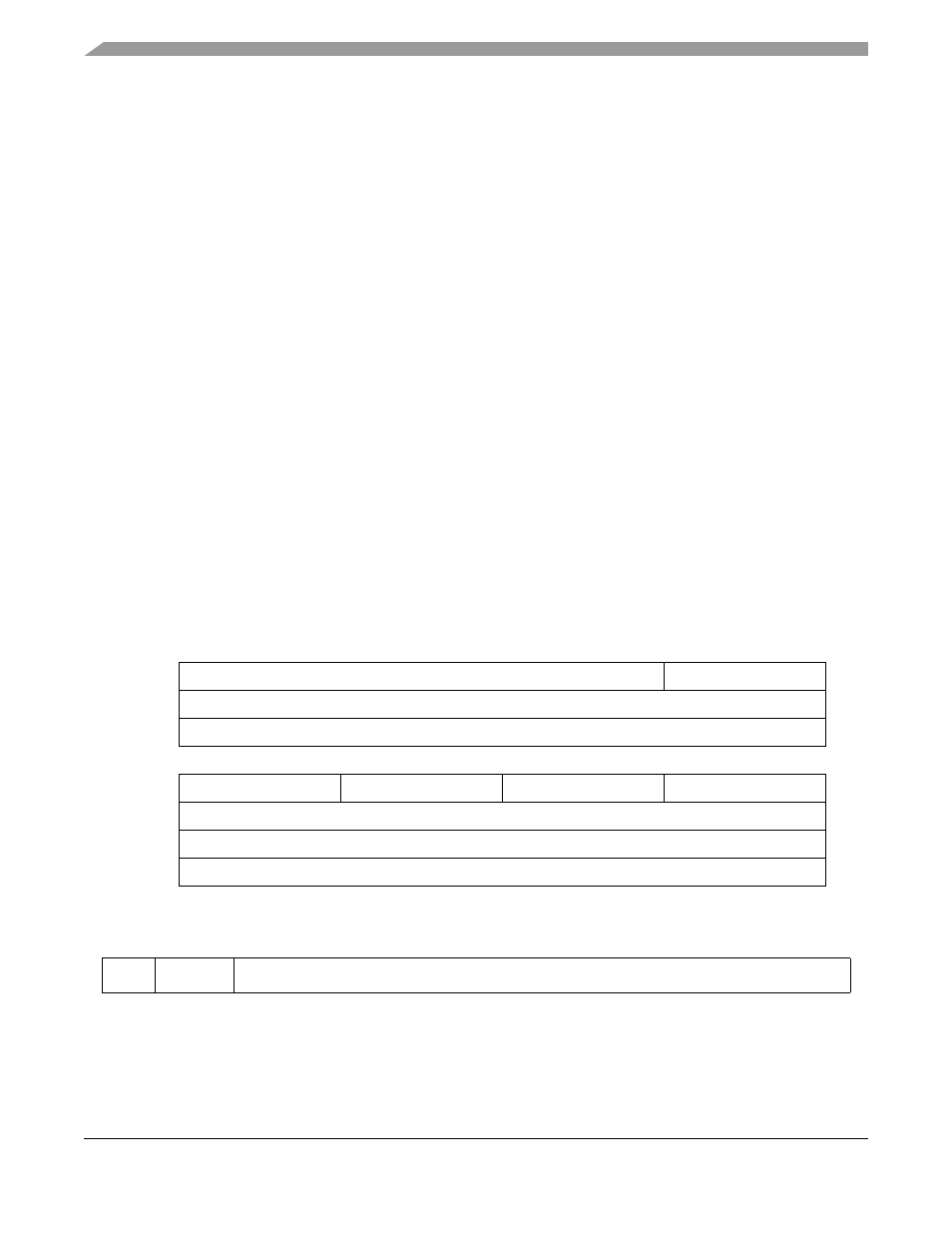

31

20

19

16

Field

—

—

Reset

0000_0000_0000_0000

R/W

R/W

15

12

11

8

7

4

3

0

Field

DMAC3

DMAC2

DMAC1

DMAC0

Reset

0000_0000_0000_0000

R/W

R/W

IPSBAR + 0x014

Figure 16-2. DMA Request Control Register (DMAREQC)

Table 16-1. DMAREQC Field Description

Bits

Name

Description

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3