7 reset, 8 interrupts, 1 gpt channel interrupts (cnf) – Motorola ColdFire MCF5281 User Manual

Page 389: 7 reset -21 20.8 interrupts -21, 1 gpt channel interrupts (cnf) -21, 1 gpt channel interrupts (c n f)

General Purpose Timer Modules (GPTA and GPTB)

Freescale Semiconductor

20-21

20.7

Reset

Reset initializes the GPT registers to a known startup state as described in

.”

20.8

Interrupts

lists the interrupt requests generated by the timer.

20.8.1

GPT Channel Interrupts (CnF)

A channel flag is set when an input capture or output compare event occurs. Clear a channel flag by writing

a 1 to it.

1

0

1

X

X

1

Out

OC

action/

OC3Dn

Output compare

(ch 3)

Pin readable only if DDR = 0

6

1

1

1

X

X

1

Out

OC

action/

OC3Dn

Output

compare/

OC3Dn

(ch 3)

Pin driven by channel OC action and

OC3Dn via channel 3 OC

(6)

1

When DDR set the pin as input (0), reading the data register will return the state of the pin. When DDR set the pin as output (1),

reading the data register will return the content of the data latch. Pin conditions such as rising or falling edges can trigger an input

capture on a pin configured as an input.

2

OMn/OLn bit pairs select the output action to be taken as a result of a successful output compare. When either OMn or OLn is

set and the IOSn bit is set, the pin is an output regardless of the state of the corresponding DDR bit.

3

Setting an OC3M bit configures the corresponding PORTTn pin to be output. OC3Mn makes the PORTTn pin an output regardless

of the data direction bit when the pin is configured for output compare (IOSn = 1). The OC3Mn bits do not change the state of the

PORTTnDDR bits.

4

X = Don’t care

5

An output compare overrides the data direction bit of the output compare pin but does not change the state of the data direction

bit. Enabling output compare disables data register drive of the pin.

6

A successful output compare on channel 3 causes an output value determined by OC3Dn value to temporarily override the output

compare pin state of any other output compare channel.The next OC action for the specific channel will still be output to the pin.

A channel 3 output compare can cause bits in the output compare 3 data register to transfer to the GPT port data register,

depending on the output compare 3 mask register.

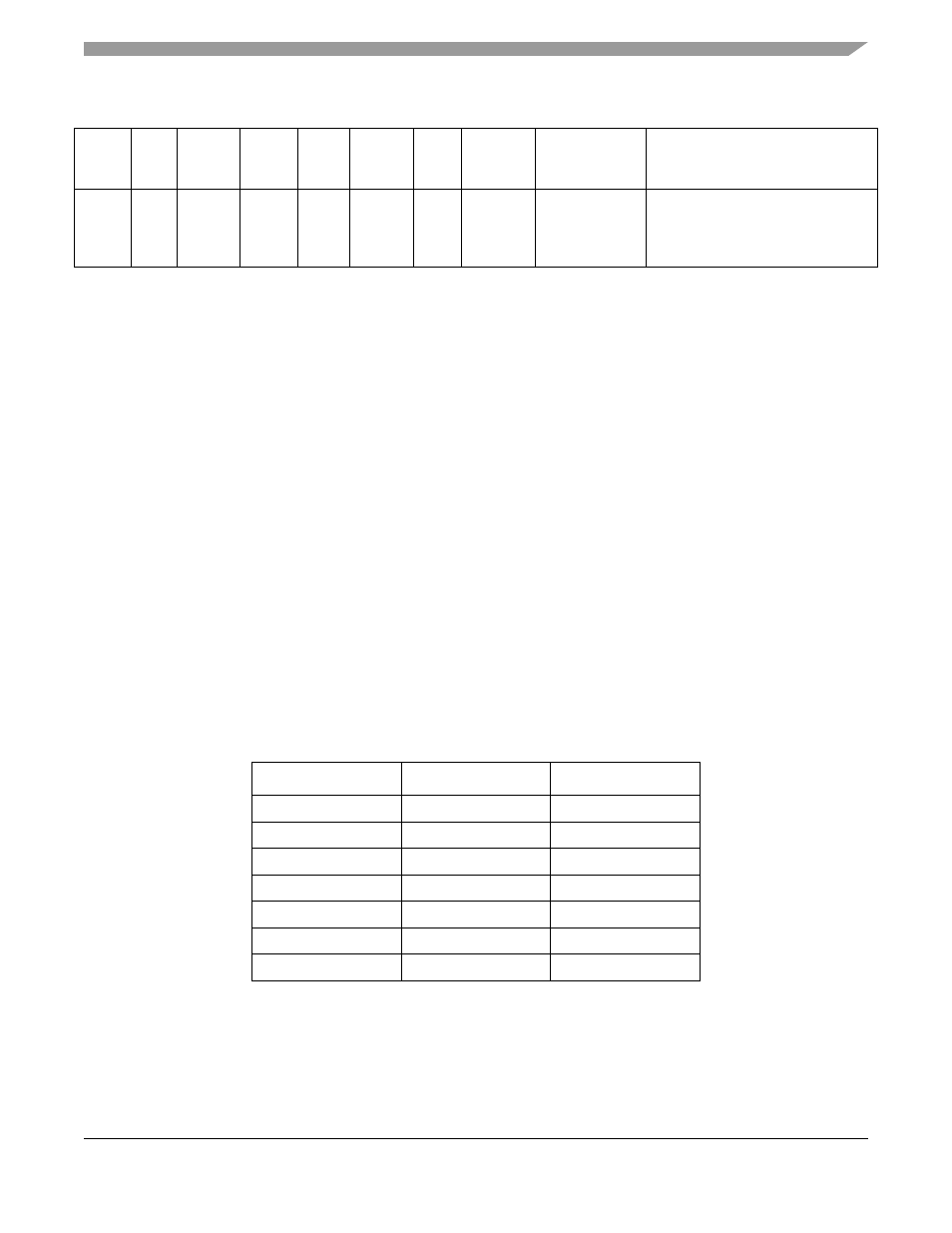

Table 20-24. GPT Interrupt Requests

Interrupt Request

Flag

Enable Bit

Channel 3 IC/OC

C3F

C3I

Channel 2 IC/OC

C2F

C2I

Channel 1 IC/OC

C1F

C1I

Channel 0 IC/OC

C0F

C0I

PA overflow

PAOVF

PAOVI

PA input

PAIF

PAI

Timer overflow

TOF

TOI

Table 20-23. GPT Settings and Pin Functions (continued)

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3