2 sram initialization, 3 sram initialization code – Motorola ColdFire MCF5281 User Manual

Page 111

Static RAM (SRAM)

Freescale Semiconductor

5-3

5.3.2

SRAM Initialization

After a hardware reset, the contents of the SRAM module are undefined. The valid bit of the RAMBAR

is cleared, disabling the module. If the SRAM requires initialization with instructions or data, the

following steps should be performed:

1. Load the RAMBAR mapping the SRAM module to the desired location within the address space.

2. Read the source data and write it to the SRAM. There are various instructions to support this

function, including memory-to-memory move instructions, or the MOVEM opcode. The

MOVEM instruction is optimized to generate line-sized burst fetches on 0-modulo-16 addresses,

so this opcode generally provides maximum performance.

3. After the data has been loaded into the SRAM, it may be appropriate to load a revised value into

the RAMBAR with a new set of attributes. These attributes consist of the write-protect and

address space mask fields.

The ColdFire processor or an external emulator using the debug module can perform these initialization

functions.

5.3.3

SRAM Initialization Code

The following code segment describes how to initialize the SRAM. The code sets the base address of the

SRAM at 0x20000000 and then initializes the SRAM to zeros.

RAMBASE

EQU $20000000

;set this variable to $20000000

RAMVALID EQU

$00000001

move.l

#RAMBASE+RAMVALID,D0

;load RAMBASE + valid bit into D0.

movec.l

D0, RAMBAR

;load RAMBAR and enable SRAM

5–1

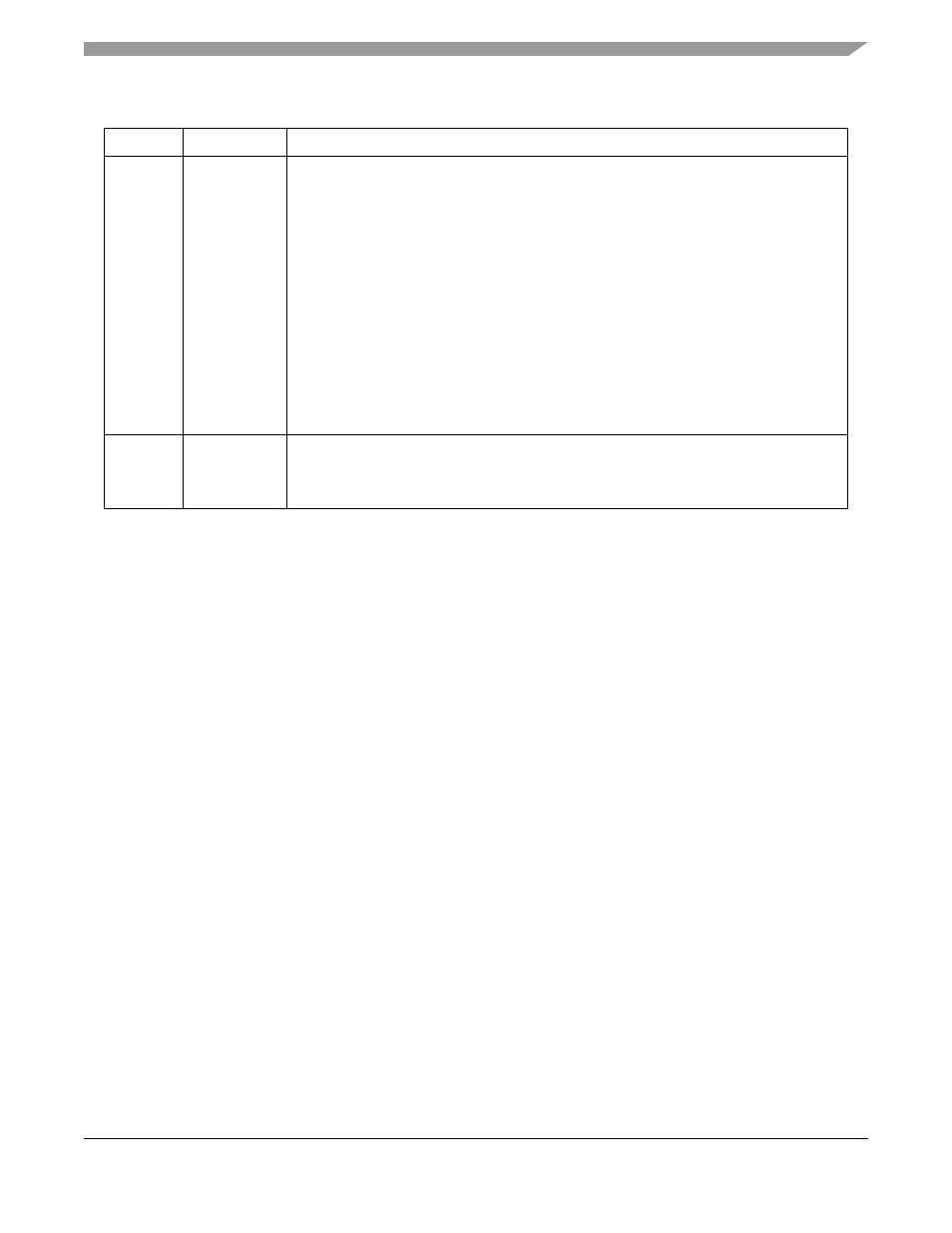

C/I, SC, SD,

UC, UD

Address space masks (ASn)

These five bit fields allow certain types of accesses to be “masked,” or inhibited from

accessing the SRAM module. The address space mask bits are:

C/I = CPU space/interrupt acknowledge cycle mask

SC = Supervisor code address space mask

SD = Supervisor data address space mask

UC = User code address space mask

UD = User data address space mask

For each address space bit:

0 An access to the SRAM module can occur for this address space

1 Disable this address space from the SRAM module. If a reference using this address

space is made, it is inhibited from accessing the SRAM module, and is processed like

any other non-SRAM reference.

These bits are useful for power management as detailed in

.”

0

V

Valid. A hardware reset clears this bit. When set, this bit enables the SRAM module;

otherwise, the module is disabled.

0 Contents of RAMBAR are not valid

1 Contents of RAMBAR are valid

Table 5-1. SRAM Base Address Register (continued)

Bits

Name

Description

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3