Table 4-7 – Motorola ColdFire MCF5281 User Manual

Page 108

Cache

4-10

Freescale Semiconductor

For instruction fetches, the fill buffer can also be used as temporary storage for line-sized bursts of

non-cacheable references under control of CACR[CEIB]. With this bit set, a non-cacheable instruction

fetch is processed, as defined by

. For this condition, the line-fill buffer is loaded and subsequent

references can hit in the buffer, but the data is never loaded into the memory array.

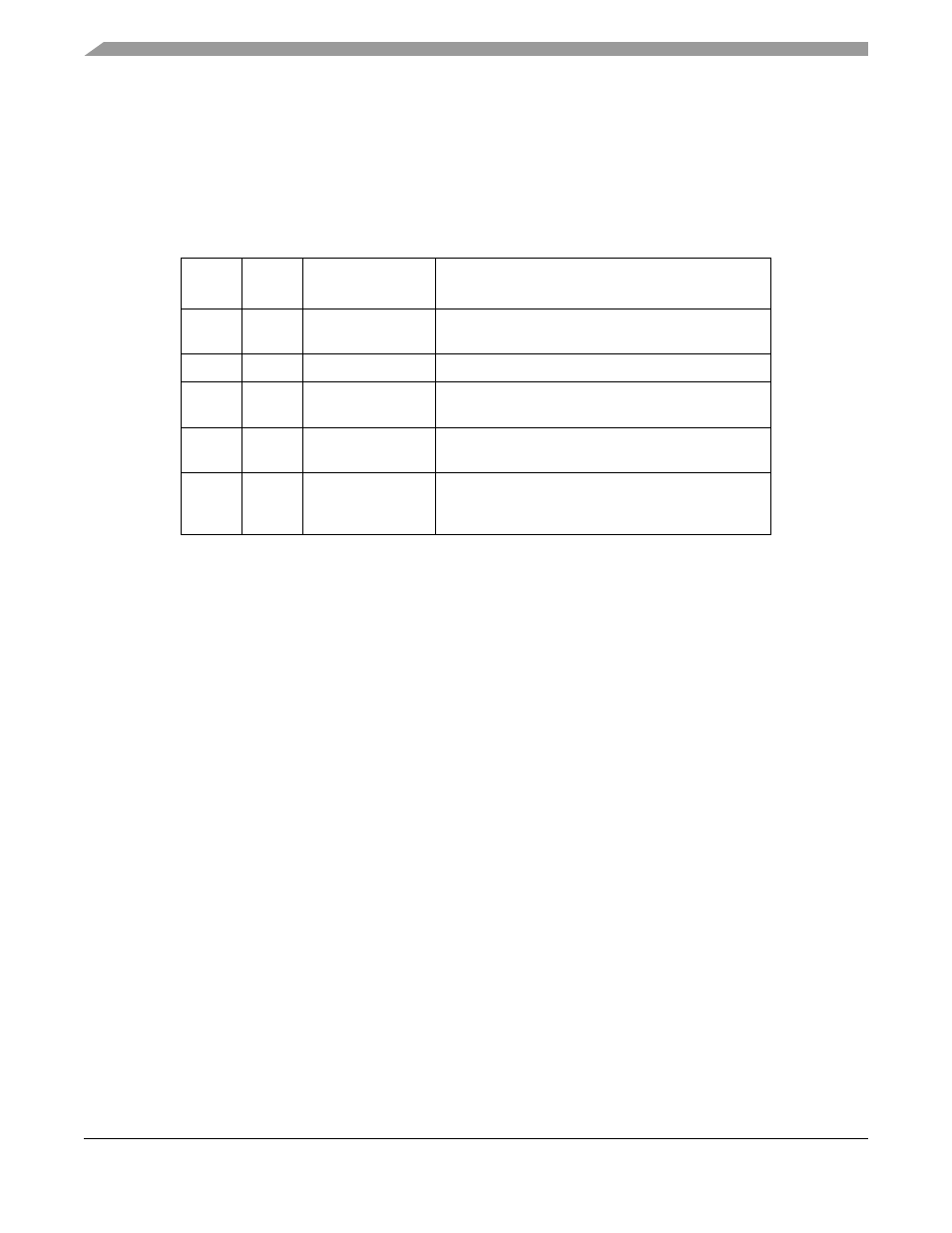

shows the relationship between CACR bits CENB and CEIB and the type of instruction fetch.

Table 4-7. Instruction Cache Operation as Defined by CACR

CACR

[CENB]

CACR

[CEIB]

Type of

Instruction Fetch

Description

0

0

N/A

Cache is completely disabled; all instruction fetches

are word or longword in size.

0

1

N/A

All instruction fetches are word or longword in size

1

X

Cacheable

and contents of the

line-fill buffer can be written into the memory array

1

0

Non-cacheable

All instruction fetches are word or longword in size,

and not loaded into the line-fill buffer

1

1

Non-cacheable

Instruction fetch size is defined by

and

loaded into the line-fill buffer, but are never written into

the memory array.

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3