6 gated time accumulation mode, 7 general-purpose i/o ports – Motorola ColdFire MCF5281 User Manual

Page 387

General Purpose Timer Modules (GPTA and GPTB)

Freescale Semiconductor

20-19

The PA overflow flag, PAOVF, is set when the PA rolls over from 0xFFFF to 0x0000. The PA overflow

interrupt enable bit, PAOVI, enables the PAOVF flag to generate interrupt requests.

NOTE

The PA can operate in event counter mode even when the GPT enable bit,

GPTEN, is clear.

20.6.6

Gated Time Accumulation Mode

Setting the PAMOD bit configures the PA for gated time accumulation operation. An active level on the

PAI pin enables a divide-by-64 clock to drive the PA. The PA edge bit, PEDGE, selects low levels or high

levels to enable the divide-by-64 clock.

The trailing edge of the active level at the PAI pin sets the PA input flag, PAIF. The PA input interrupt

enable bit, PAI, enables the PAIF flag to generate interrupt requests.

NOTE

The PAI input and GPT channel 3 use the same pin. To use the PAI input,

disconnect it from the output logic by clearing the channel 3 output mode

and output level bits, OM3 and OL3. Also clear the channel 3 output

compare mask bit, OC3M3.

The PA counter register, GPTPACNT, reflects the number of pulses from the divide-by-64 clock since the

last reset.

NOTE

The GPT prescaler generates the divide-by-64 clock. If the timer is not

active, there is no divide-by-64 clock.

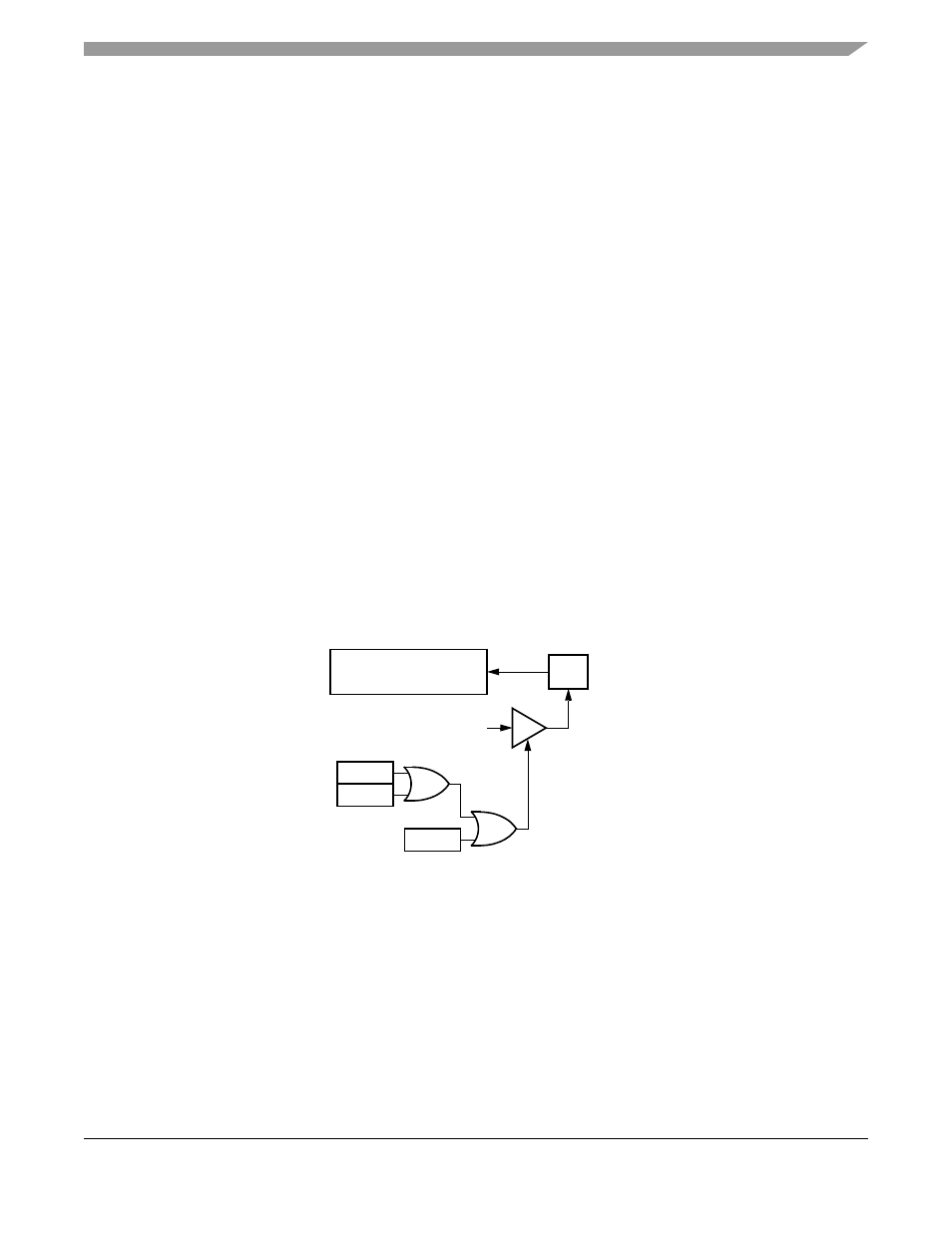

Figure 20-22. Channel 3 Output Compare/Pulse Accumulator Logic

20.6.7

General-Purpose I/O Ports

An I/O pin used by the timer defaults to general-purpose I/O unless an internal function which uses that

pin is enabled.

The PORTTn pins can be configured for either an input capture function or an output compare function.

The IOSn bits in the GPT IC/OC select register configure the PORTTn pins as either input capture or

output compare pins.

PAD

OM3

OL3

CHANNEL 3 OUTPUT COMPARE

PULSE

ACCUMULATOR

OC3M3

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3