3 fifo, 3 fifo -21 – Motorola ColdFire MCF5281 User Manual

Page 441

UART Modules

Freescale Semiconductor

23-21

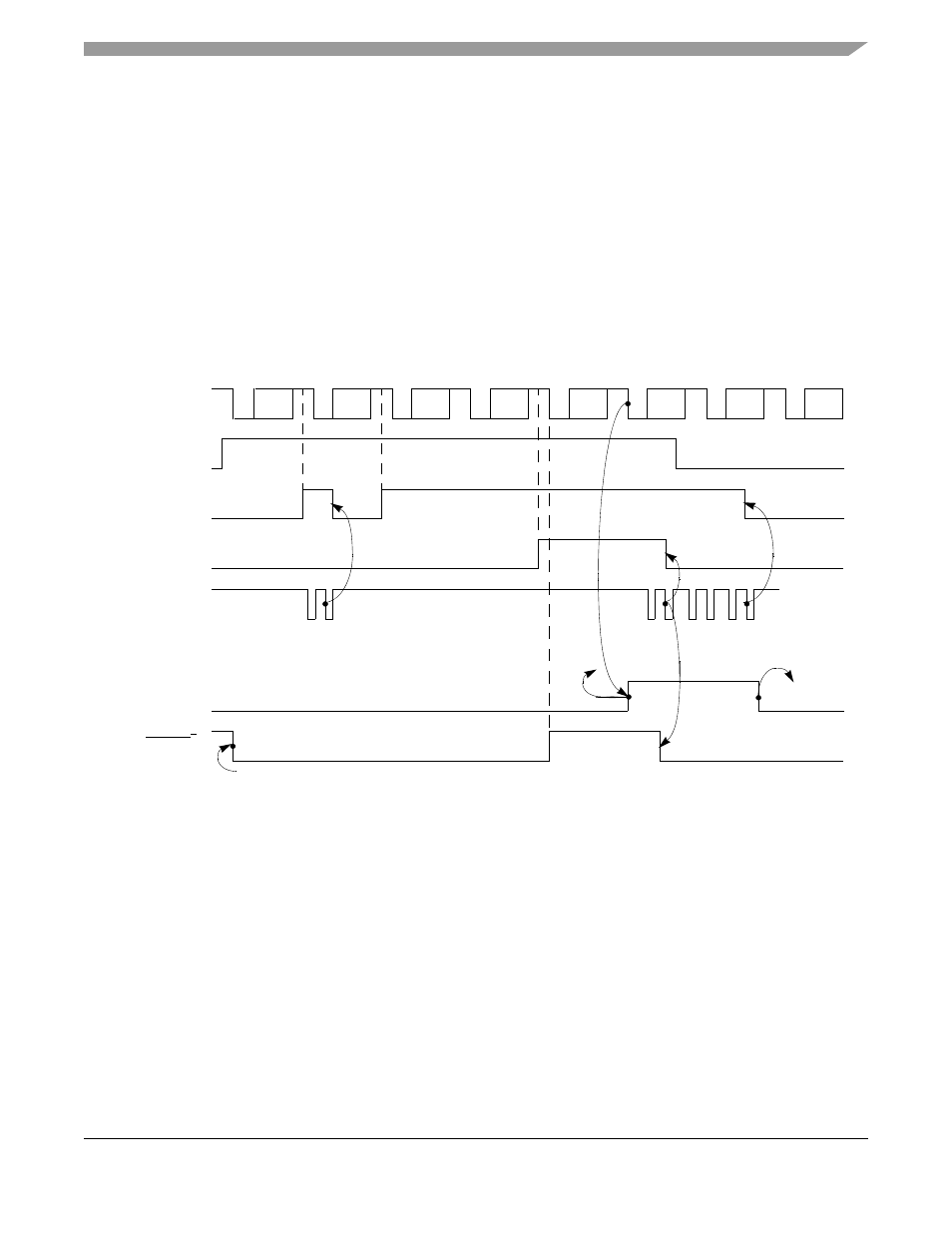

framing error, overrun error, and received break conditions set the respective PE, FE, OE, and RB error

and break flags in the USRn at the received character boundary. They are valid only if USRn[RXRDY] is

set.

If a break condition is detected (URXDn is low for the entire character including the stop bit), a character

of all 0s loads into the receiver holding register and USRn[RB,RXRDY] are set. URXDn must return to a

high condition for at least one-half bit time before a search for the next start bit begins.

The receiver detects the beginning of a break in the middle of a character if the break persists through the

next character time. The receiver places the damaged character in the Rx FIFO and sets the corresponding

USRn error bits and USRn[RXRDY]. Then, if the break lasts until the next character time, the receiver

places an all-zero character into the Rx FIFO and sets USRn[RB,RXRDY].

shows receiver functional timing.

Figure 23-20. Receiver Timing Diagram

23.4.2.3

FIFO

The FIFO is used in the UART’s receive buffer logic. The FIFO consists of three receiver holding registers.

The receive buffer consists of the FIFO and a receiver shift register connected to the URXDn (see

). Data is assembled in the receiver shift register and loaded into the top empty receiver

holding register position of the FIFO. Therefore, data flowing from the receiver to the CPU is

quadruple-buffered.

In addition to the data byte, three status bits—parity error (PE), framing error (FE), and received break

(RB)—are appended to each data character in the FIFO; overrun error (OE) is not appended. By

C1

C2

C4

C6

C7

C8

C3

C5

C6, C7, and C8 is lost

(C2)

Status

Data

(C3)

Status

Data

(C4)

Status

Data

C5 is

lost

Reset by

command

Receiver

Enabled

USRn[RXRDY]

Overrun

Internal

module

select

USRn[FFULL]

(C1)

Status

Data

USRn[OE]

Automatically asserted

when ready to receive

Manually asserted first time,

automatically negated if overrun occurs

UOP0[RTS] = 1

1

UMR2n[RXRTS] = 1

URXDn

URTSn

1

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3