B.2 changes between rev. 0.1 and rev. 1 – Motorola ColdFire MCF5281 User Manual

Page 738

Revision History

B-2

Freescale Semiconductor

B.2

Changes Between Rev. 0.1 and Rev. 1

Changed “RAS0” and “RAS1” to “SDRAM_CS0” and “SDRAM_CS1.”

Added

.

Changed max input high voltage to 5.25 V.

Changed “System Integration Module” to “System Control Module.”

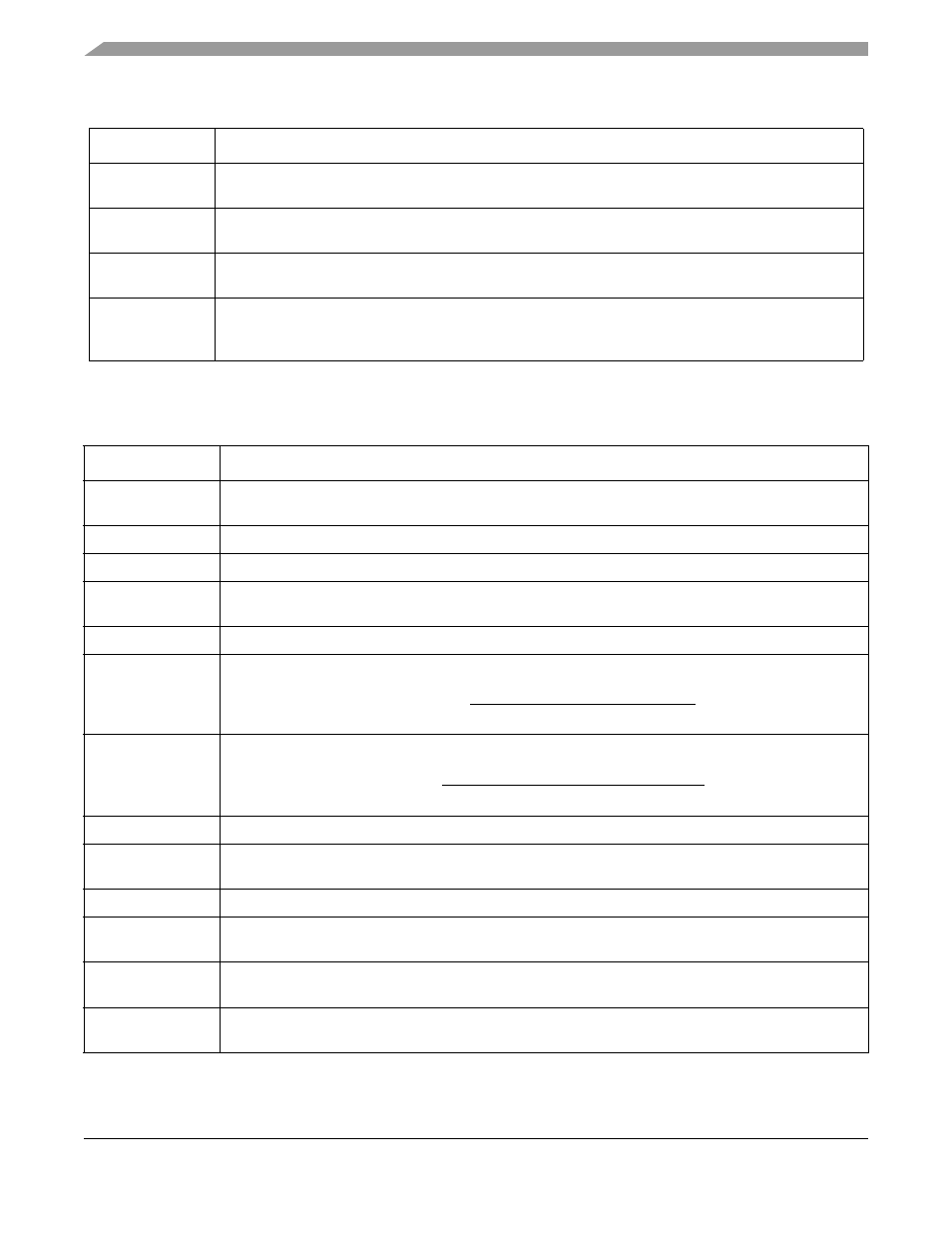

Table B-2. Rev. 0.1 to Rev. 1 Changes

Location

Description

Replaced

with a more accurate block diagram.

Enhanced discussion of Flash blocks.

Added “Note:

Enabling Flash security will disable BDM communications.”

Added “Note:

When Flash security is enabled, the chip will boot in single chip mode regardless

of the external reset configuration.”

Changed text in Step 1 to read “If f

SYS

÷

2 is greater than 12.8 MHz, PRDIV8 = 1; otherwise PRDIV8 = 0.”

Changed equation in Step 2 to the following:

Changed equation in Step 3 to the following:

Changed equations in example to reflect revisions above.

Changed text to read “So, for f

SYS

= 66 MHz, writing 0x54 to CFMCLKD will set FCLK to 196.43 kHz which

is a valid frequency for the timing of program and erase functions.”

Changed text to read “Consider the follwoing example for f

SYS

= 66 MHz.”

Added “Page erase verify” category.

Added “Page erase verify” category and description.

Added “Access error” row.

Table B-1. Rev. 0 to Rev. 0.1 Changes (continued)

Location

Description

f

SYS

2 x 200kHz x (1 + (PRDIV8 x 7))

DIV[5:0] =

f

SYS

2 x (DIV[5:0] + 1) x (1 + (PRDIV8 x 7))

f

CLK

=

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3