12 gpt flag register 1 (gptflg1), 13 gpt flag register 2 (gptflg2) – Motorola ColdFire MCF5281 User Manual

Page 380

General Purpose Timer Modules (GPTA and GPTB)

20-12

Freescale Semiconductor

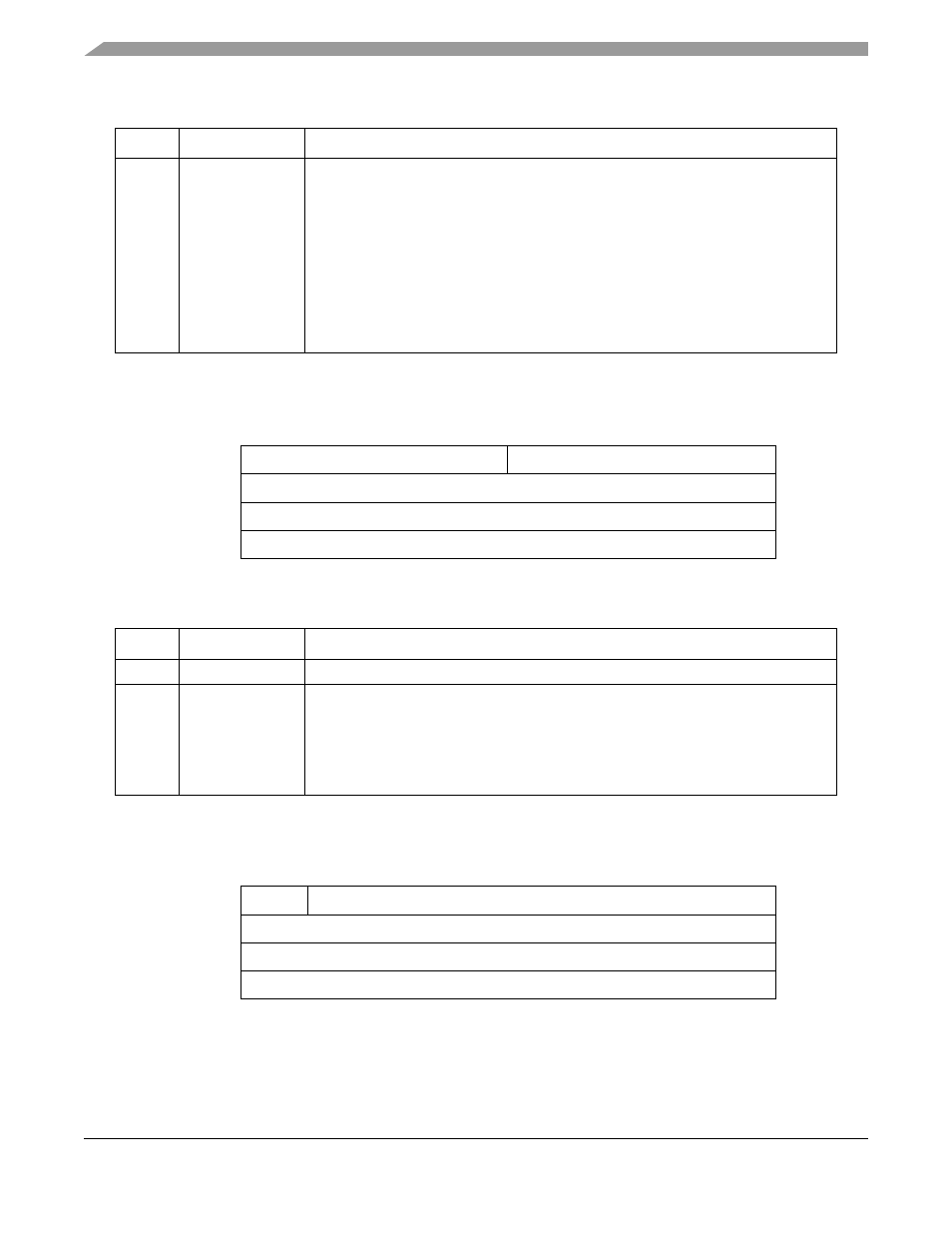

20.5.12 GPT Flag Register 1 (GPTFLG1)

20.5.13 GPT Flag Register 2 (GPTFLG2)

2–0

PRn

Prescaler bits. Select the prescaler divisor for the GPT counter.

000 Prescaler divisor 1

001 Prescaler divisor 2

010 Prescaler divisor 4

011 Prescaler divisor 8

100 Prescaler divisor 16

101 Prescaler divisor 32

110 Prescaler divisor 64

111 Prescaler divisor 128

Note: The newly selected prescaled clock does not take effect until the next

synchronized edge of the prescaled clock when the clock count transitions to 0x0000.)

7

6

5

4

3

0

Field

—

CF

Reset

0000_0000

R/W

R/W

Address

IPSBAR + 0x1A_000E, 0x1B_000E

Figure 20-14. GPT Flag Register 1 (GPTFLG1)

Table 20-15. GPTFLG1 Field Descriptions

Bit(s)

Name

Description

7–4

—

Reserved, should be cleared.

3–0

CnF

Channel flags. A channel flag is set when an input capture or output compare event

occurs. These bits are read anytime, write anytime (writing 1 clears the flag, writing 0

has no effect).

Note: When the fast flag clear all bit, GPTSCR1[TFFCA], is set, an input capture read

or an output compare write clears the corresponding channel flag. When a channel

flag is set, it does not inhibit subsequent output compares or input captures.

7

6

5

4

3

0

Field

TOF

—

Reset

0000_0000

R/W

R/W

Address

IPSBAR + 0x1A_000F, 0x1B_000F

Figure 20-15. GPT Flag Register 2 (GPTFLG2)

Table 20-14. GPTSCR2 Field Descriptions (continued)

Bit(s)

Name

Description

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3