Motorola ColdFire MCF5281 User Manual

Page 660

Debug Support

30-42

Freescale Semiconductor

Exception ProcessingPST = 0xC,{PST = 0xB,DD = destination},// stack frame

{PST = 0xB,DD = destination},// stack frame

{PST = 0xB,DD = source},// vector read

PST = 0x5,{PST = [0x9AB],DD = target}// handler PC

The PST/DDATA specification for the reset exception is shown below:

Exception ProcessingPST = 0xC,

PST = 0x5,{PST = [0x9AB],DD = target}// handler

PC

The initial references at address 0 and 4 are never captured nor displayed since these accesses are treated

as instruction fetches.

rts

PST = 0x1, {PST = 0xB, DD = source operand},

PST = 0x5, {PST = [0x9AB], DD = target address}

scc

Dx

PST = 0x1

sub.l

PST = 0x1, {PST = 0xB, DD = source operand}

sub.l

Dy,

PST = 0x1, {PST = 0xB, DD = source}, {PST = 0xB, DD = destination}

subi.l

#imm,Dx

PST = 0x1

subq.l

#imm,

PST = 0x1, {PST = 0xB, DD = source}, {PST = 0xB, DD = destination}

subx.l

Dy,Dx

PST = 0x1

swap

Dx

PST = 0x1

trap

#imm

PST = 0x1

3

trapf

PST = 0x1

tst.b

PST = 0x1, {PST = 0x8, DD = source operand}

tst.l

PST = 0x1, {PST = 0xB, DD = source operand}

tst.w

PST = 0x1, {PST = 0x9, DD = source operand}

unlk

Ax

PST = 0x1, {PST = 0xB, DD = destination operand}

wddata.b

PST = 0x4, {PST = 0x8, DD = source operand

wddata.l

PST = 0x4, {PST = 0xB, DD = source operand

wddata.w

PST = 0x4, {PST = 0x9, DD = source operand

1

For JMP and JSR instructions, the optional target instruction address is displayed only for those effective address

fields defining variant addressing modes. This includes the following

(d8,PC,Xi).

2

For Move Multiple instructions (MOVEM), the processor automatically generates line-sized transfers if the operand

address reaches a 0-modulo-16 boundary and there are four or more registers to be transferred. For these line-sized

transfers, the operand data is never captured nor displayed, regardless of the CSR value.

The automatic line-sized burst transfers are provided to maximize performance during these sequential memory

access operations.

3

During normal exception processing, the PST output is driven to a 0xC indicating the exception processing state. The

exception stack write operands, as well as the vector read and target address of the exception handler may also be

displayed.

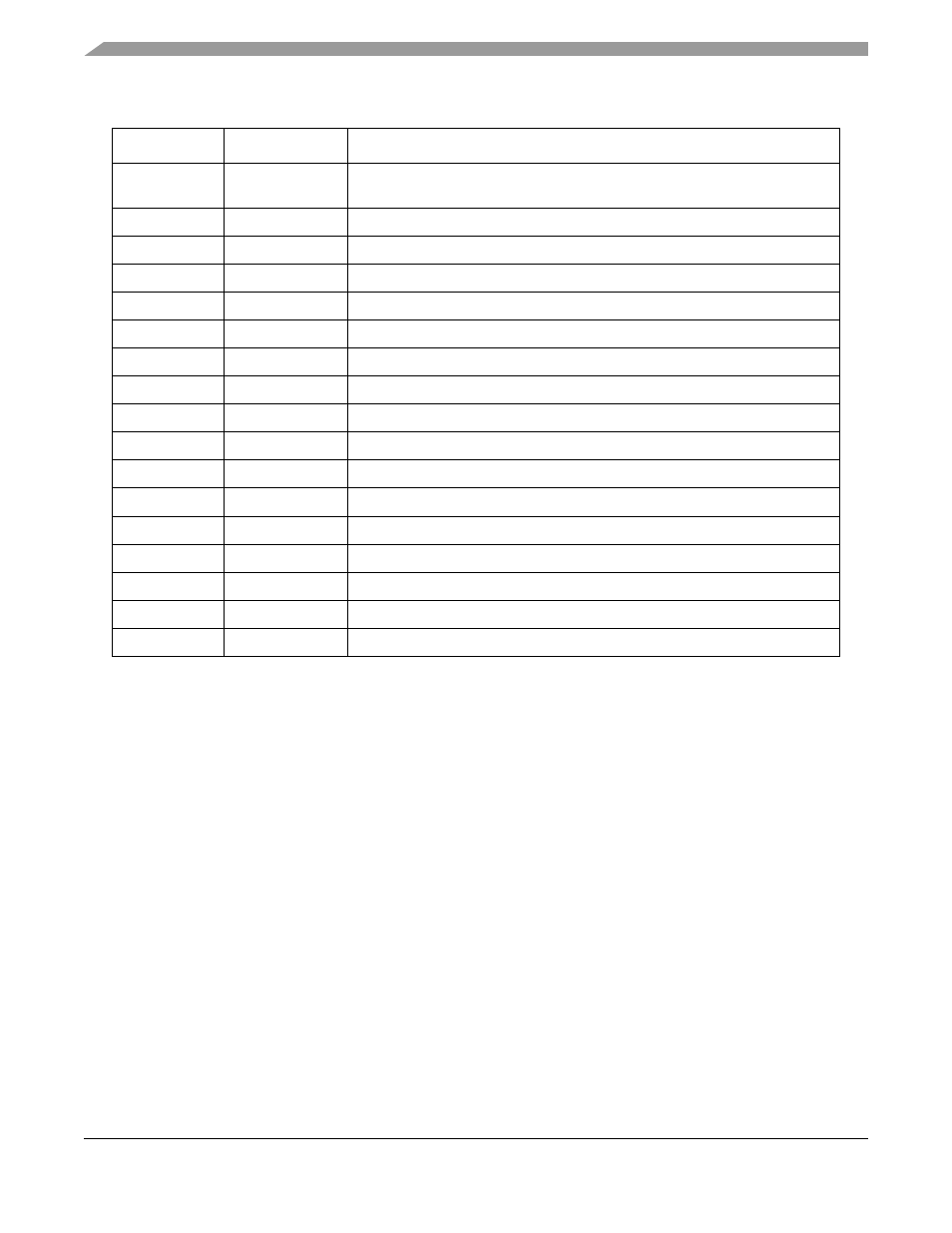

Table 30-22. PST/DDATA Specification for User-Mode Instructions (continued)

Instruction

Operand Syntax

PST/DDATA

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3