3 general synchronous operation guidelines, 1 address multiplexing, 3 general synchronous operation guidelines -9 – Motorola ColdFire MCF5281 User Manual

Page 281: 1 address multiplexing -9

Synchronous DRAM Controller Module

Freescale Semiconductor

15-9

15.2.3

General Synchronous Operation Guidelines

To reduce system logic and to support a variety of SDRAM sizes, the DRAM controller provides SDRAM

control signals as well as a multiplexed row address and column address to the SDRAM.

15.2.3.1

Address Multiplexing

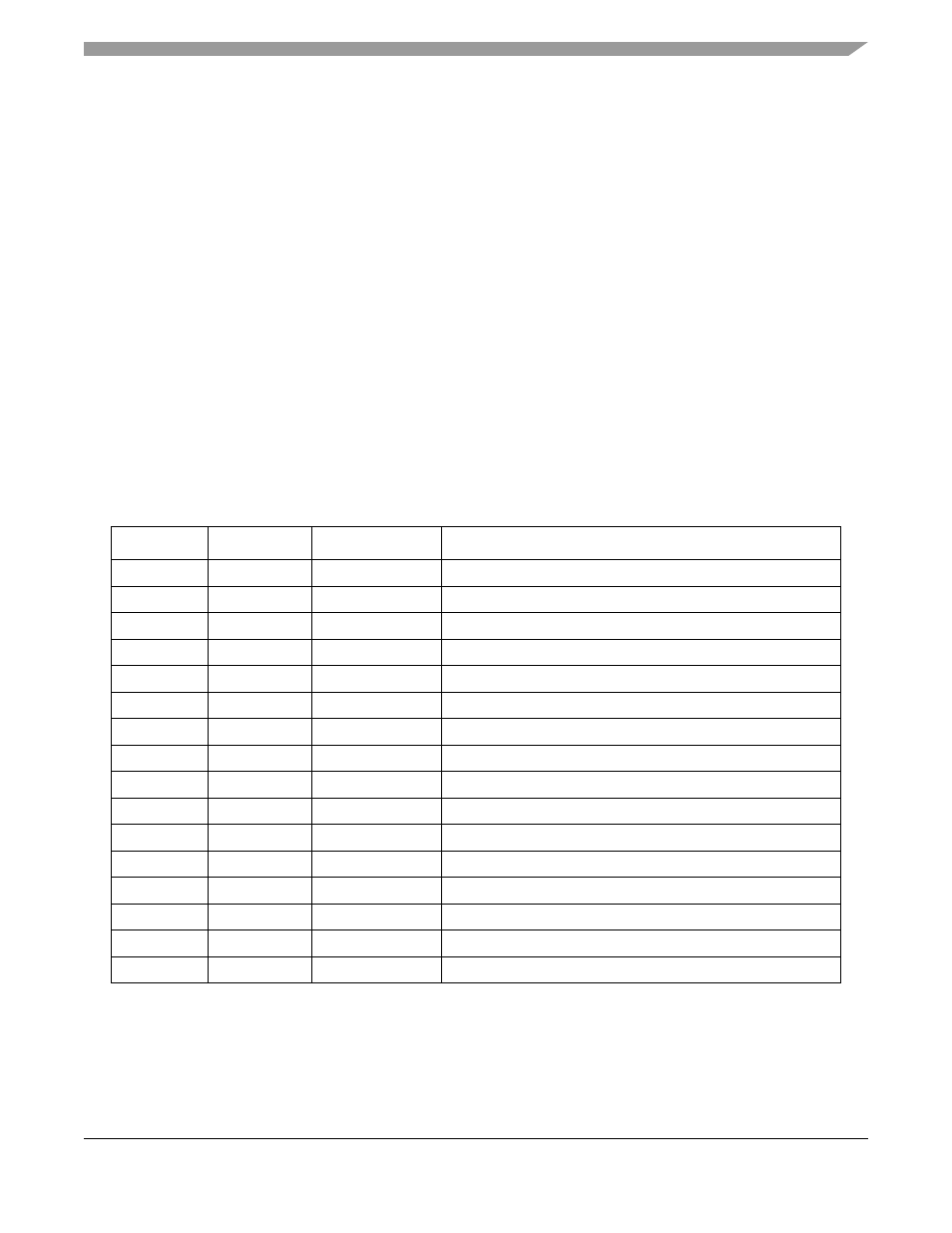

shows the generic address multiplexing scheme for SDRAM configurations. All possible

address connection configurations can be derived from this table.

NOTE

Because the processor has 24 extermal address lines, the maximum

SDRAM address size is 128 Mbits.

The following tables provide a more comprehensive, step-by-step way to determine the correct address

line connections for interfacing the ColdFire processor to the SDRAM. To use the tables, find the one that

corresponds to the number of column address lines on the SDRAM and to the port size as seen by the

processor, which is not necessarily the SDRAM port size. For example, if two 1M x 16-bit SDRAMs

together form a 1M x 32-bit memory, the port size is 32 bits. Most SDRAMs likely have fewer address

lines than are shown in the tables, so follow only the connections shown until all SDRAM address lines

are connected.

Table 15-7. Generic Address Multiplexing Scheme

Address Pin

Row Address

Column Address

Notes Relating to Port Sizes

17

17

0

8-bit port only

16

16

1

8- and 16-bit ports only

15

15

2

14

14

3

13

13

4

12

12

5

11

11

6

10

10

7

9

9

8

17

17

16 32-bit

port

only

18

18

17

16-bit port only or 32-bit port with only 8 column address lines

19

19

18

16-bit port only when at least 9 column address lines are used

20

20

19

21

21

20

22

22

21

23

23

22

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3