2 qadc status register 1 (qasr1), 2 qadc status register 1 (qasr1) -23, Stop mode resets this register – Motorola ColdFire MCF5281 User Manual

Page 561

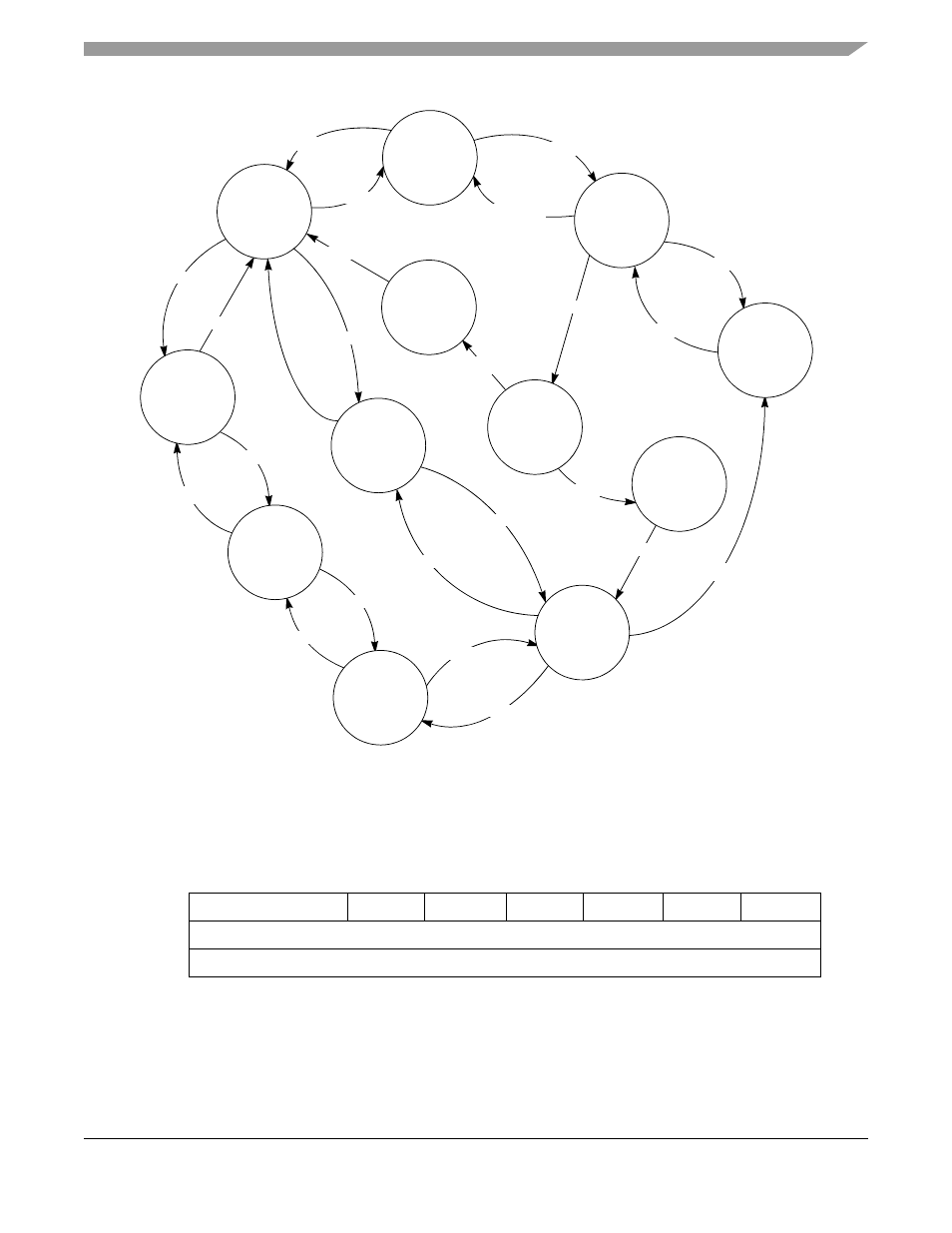

Queued Analog-to-Digital Converter (QADC)

Freescale Semiconductor

28-23

Figure 28-12. Queue Status Transition

28.6.6.2

QADC Status Register 1 (QASR1)

Stop mode resets this register .

15

14

13

12

11

10

9

8

Field

—

CWPQ15

CWPQ14

CWPQ13

CWPQ12

CWPQ11

CWPQ10

Reset

0011_1111

R/W:

R

Q1 Idle/

Q2 Active

Q1 Idle/

Q2 Idle

Q1 Active/

Q2 Idle

Q1 Paused/

Q2 Idle

Q1 Active/

Q2 Suspended

Q1 Active/

Q2 Paused

Q1 Paused/

Q2 Active

Q1 Idle/

Q2 Paused

Q1 Paused/

Q2 Paused

Q1 Active/

Q2 Trigger

Pending

Q1 Paused/

Q2 Trigger

Pending

(Temporary)

Q2 Complete

Delayed Transition

Q1 Pause Bit Set

Q2 Trigger Event

Q1 Trigger Event

Q1 Pause Bit Set

Q1 Complete

Q1 Trigger Event

Q1 Complete

Delayed Transition

Q1 Complete

Q1 Pause Bit Set

Q1 Trigger Event

Q2 Complete

Q2 Pause Bit Set

Q2 Trigger Event

Q1 Trigger Event

Q1 Complete

Q1 Trigger Event

Q1 Pause Bit Set

Q2 Pause Bit Set

Q2 Trigger Event

Q1 Idle/

Q2 Trigger

Pending

(Temporary)

Q1 Trigger Event

Q2 Trigger Event

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3