Motorola ColdFire MCF5281 User Manual

Page 716

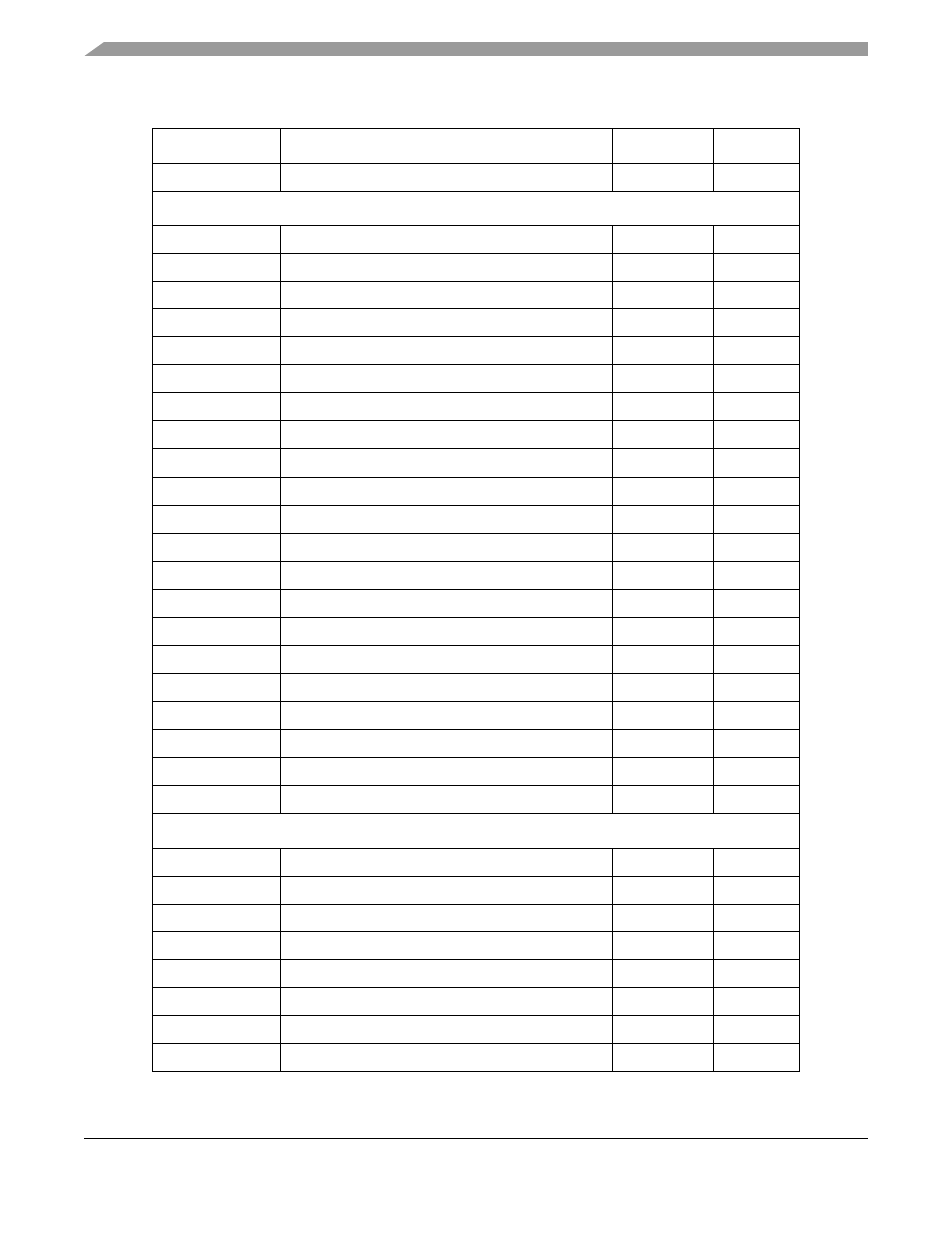

Register Memory Map

A-4

Freescale Semiconductor

IPSBAR + 0x054

DRAM Mask Register Block 1

DMR1

32

Chip Select Registers

IPSBAR + 0x080

Chip Select Address Register 0

CSAR0

16

IPSBAR + 0x084

Chip Select Mask Register 0

CSMR0

32

IPSBAR + 0x08A

Chip Select Control Register 0

CSCR0

16

IPSBAR + 0x08C

Chip Select Address Register 1

CSAR1

16

IPSBAR + 0x090

Chip Select Mask Register 1

CSMR1

32

IPSBAR + 0x096

Chip Select Control Register 1

CSCR1

16

IPSBAR + 0x098

Chip Select Address Register 2

CSAR2

16

IPSBAR + 0x09C

Chip Select Mask Register 2

CSMR2

32

IPSBAR + 0x0A2

Chip Select Control Register 2

CSCR2

16

IPSBAR + 0x0A4

Chip Select Address Register 2

CSAR3

16

IPSBAR + 0x0A8

Chip Select Mask Register 3

CSMR3

32

IPSBAR + 0x0AE

Chip Select Control Register 3

CSCR3

16

IPSBAR + 0x0B0

Chip Select Address Register 4

CSAR4

16

IPSBAR + 0x0B4

Chip Select Mask Register 4

CSMR4

32

IPSBAR + 0x0BA

Chip Select Control Register 4

CSCR4

16

IPSBAR + 0x0BC

Chip Select Address Register 5

CSAR5

16

IPSBAR + 0x0C0

Chip Select Mask Register 5

CSMR5

32

IPSBAR + 0x0C6

Chip Select Control Register 5

CSCR5

16

IPSBAR + 0x0C8

Chip Select Address Register 6

CSAR6

16

IPSBAR + 0x0CC

Chip Select Mask Register 6

CSMR6

32

IPSBAR + 0x0D2

Chip Select Control Register 6

CSCR6

16

DMA Registers

IPSBAR + 0x100

Source Address Register 0

SAR0

32

IPSBAR + 0x104

Destination Address Register 0

DAR0

32

IPSBAR + 0x108

DMA Control Register 0

DCR0

32

IPSBAR + 0x10C

Byte Count Register 0

BCR0

1

32

IPSBAR + 0x110

DMA Status Register 0

DSR0

8

IPSBAR + 0x140

Source Address Register 1

SAR1

32

IPSBAR + 0x144

Destination Address Register 1

DAR1

32

IPSBAR + 0x148

DMA Control Register 1

DCR1

32

Table A-3. Register Memory Map (continued)

Address

Name

Mnemonic

Size

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3