3 core reset status register (crsr), 4 core watchdog control register (cwcr) – Motorola ColdFire MCF5281 User Manual

Page 157

System Control Module (SCM)

Freescale Semiconductor

8-5

8.4.3

Core Reset Status Register (CRSR)

The CRSR contains a bit for two of the reset sources to the CPU. A bit set to 1 indicates the last type of

reset that occurred. The CRSR is updated by the control logic when the reset is complete. Only one bit is

set at any one time in the CRSR. The register reflects the cause of the most recent reset. To clear a bit, a

logic 1 must be written to the bit location; writing a zero has no effect.

NOTE

The reset status register (RSR) in the reset controller module (see

Chapter 29, “Reset Controller Module

”) provides indication of all reset

sources except the core watchdog timer.

8.4.4

Core Watchdog Control Register (CWCR)

The core watchdog timer prevents system lockup if the software becomes trapped in a loop with no

controlled exit. The core watchdog timer can be enabled or disabled through CWCR[CWE]. By default it

is disabled. If enabled, the watchdog timer requires the periodic execution of a core watchdog servicing

sequence. If this periodic servicing action does not occur, the timer times out, resulting in a watchdog timer

interrupt. If the timer times out and the core watchdog transfer acknowledge enable bit (CWCR[CWTA])

is set, a watchdog timer interrupt is asserted. If a core watchdog timer interrupt acknowledge cycle has not

occurred after another timeout, CWT TA is asserted in an attempt to allow the interrupt acknowledge cycle

to proceed by terminating the bus cycle. The setting of CWCR[CWTAVAL] indicates that the watchdog

timer TA was asserted.

NOTE

The core watchdog timer is available to provide compatibility with the

watchdog timer implemented on previous ColdFire devices. However, there

is a second watchdog timer available that has new features. See

” for more information.

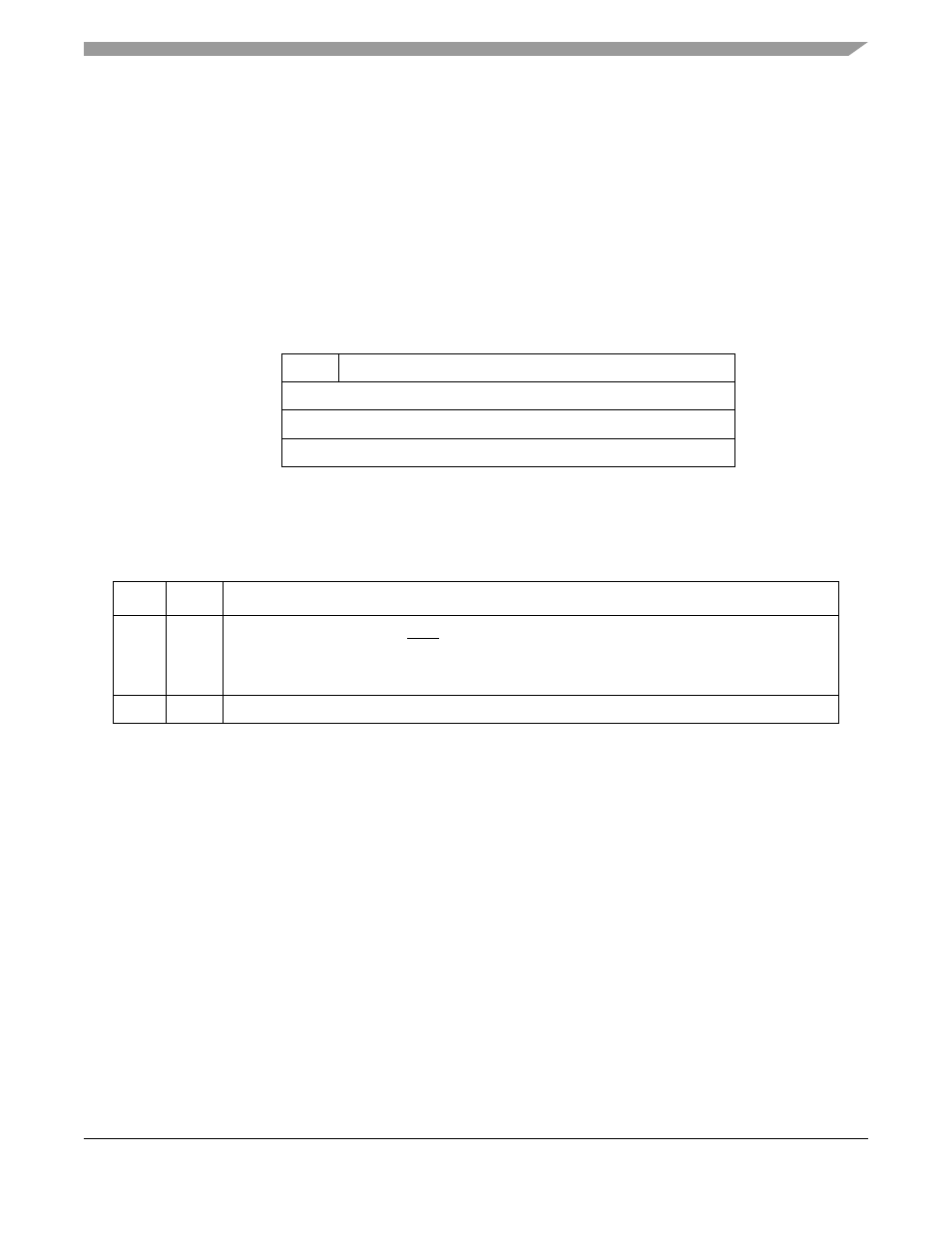

7

6

5

4

0

Field

EXT

—

Reset

See Note

R/W

R/W

Address

IPSBAR + 0x010

Note: The reset value of EXT and CWDR depend on the last reset

source. All other bits are initialized to zero.

Figure 8-3. Core Reset Status Register (CRSR)

Table 8-4. CRSR Field Descriptions

Bits

Name

Description

7

EXT

External reset.

1 An external device driving RSTI caused the last reset. Assertion of reset by an external device

causes the processor core to initiate reset exception processing. All registers are forced to their

initial state.

6-0

—

Reserved.

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3