3 line write bus cycles, 3 line write bus cycles -12 – Motorola ColdFire MCF5281 User Manual

Page 236

External Interface Module (EIM)

13-12

Freescale Semiconductor

.

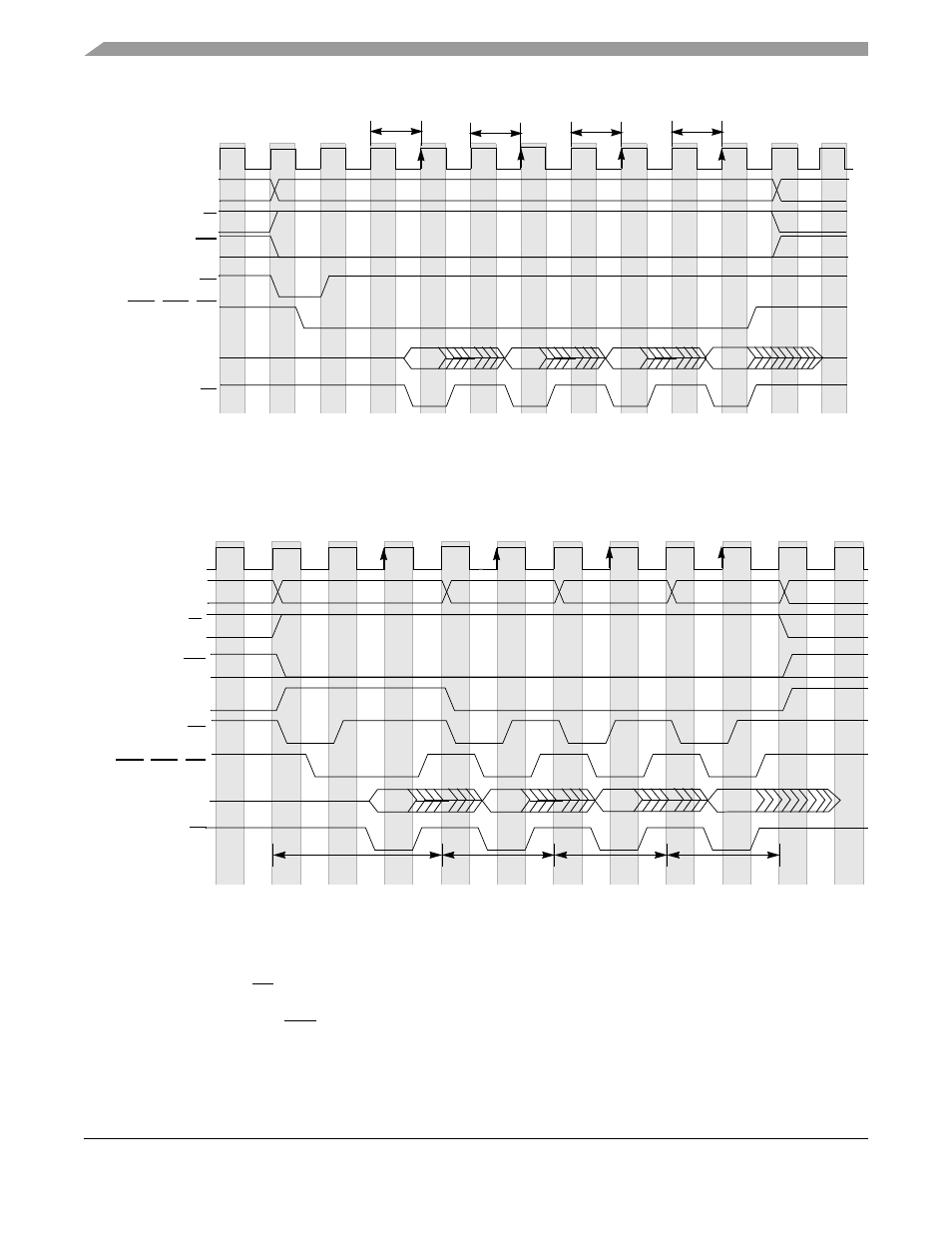

Figure 13-14. Line Read Burst (3-2-2-2), External Termination

shows a burst-inhibited line read access with fast termination. The external device executes

a basic read cycle while determining that a line is being transferred. The external device uses fast

termination for subsequent transfers.

Figure 13-15. Line Read Burst-Inhibited, Fast Termination, External Termination

13.4.7.3

Line Write Bus Cycles

shows a line access write with zero wait states. It begins like a basic write bus cycle with data

driven one clock after TS. The next pipelined burst data is driven a cycle after the write data is registered

(on the rising edge of S6). Each subsequent burst takes a single cycle. Note that as with the line read

example in

, CSn remain asserted throughout the burst transfer. This example shows the

behavior of the address lines for both internal and external termination. Note that when external

termination is used, the address lines change with SIZ[1:0].

R/W

TIP

TS

CSn, BSn, OE

D[31:0]

TA

Read

S0 S1 S2 S3

S4 S5

S10

S9

S8

S7

S6

S11

S12

S13

WS

WS

WS

WS

Read

Read

Read

CLKOUT

A[31:0], SIZ[1:0]

A[31:0]

R/W

TIP

SIZ[1:0]

TS

D[31:0]

TA

Line

Longword

Basic

Fast Fast

Fast

A[3:2] = 00

A[3:2] = 01

A[3:2] = 10

A[3:2] = 11

S0

S1

S2 S3 S4 S5 S0 S1 S4 S5

S0 S1 S4

S5

S0 S1 S4 S5

S7

S6

Read

Read

Read

Read

CLKOUT

CSn, BSn, OE

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3