Appendix b revision history, B.1 changes between rev. 0 and rev. 0.1, Appendix b – Motorola ColdFire MCF5281 User Manual

Page 737: Revision history

Freescale Semiconductor

B-1

Appendix B

Revision History

This appendix lists major changes between versions of the MCF5282UM document.

B.1

Changes Between Rev. 0 and Rev. 0.1

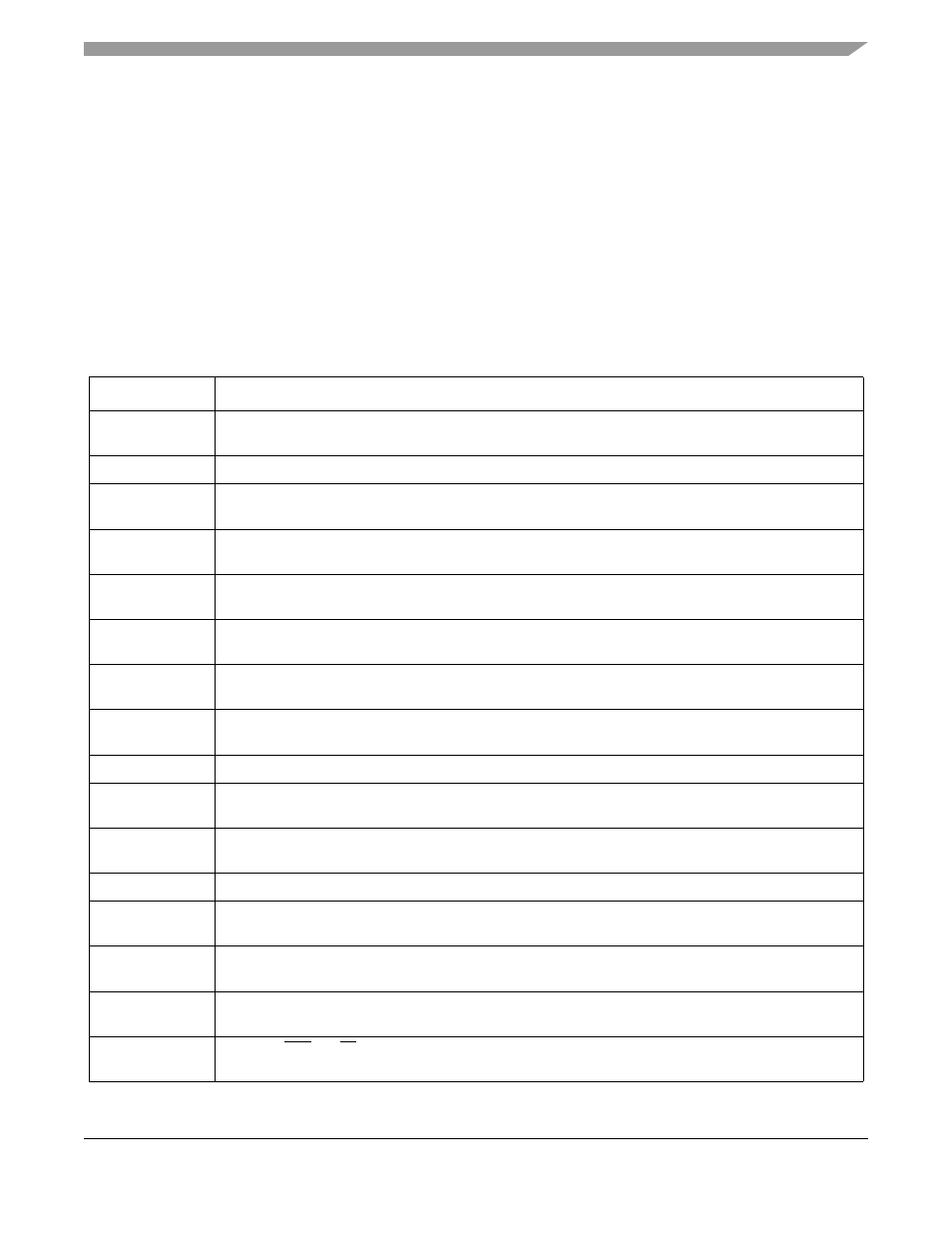

Table B-1. Rev. 0 to Rev. 0.1 Changes

Location

Description

Title page

Changed title from “MCF5282 ColdFire

®

Integrated Microprocessor User’s Manual” to “MCF5282

ColdFire

®

Microcontroller User’s Manual.”

Added “This product incorporates SuperFlash® technology licensed from SST.”

Changed equation in footnote to f

sys

= f

ref

×

2(MFD + 2)/2 exp RFD; f

ref

×

2(MFD + 2)

≤

80 MHz, f

sys

≤

66

MHz.

Multiplied all PLL frequencies in table by 2.

Changed DTMRx to DTIMx.

Changed bit numbers from 63–32 to 31–0.

Changed bit numbers from 63–32 to 31–0.

Changed bit numbers from 63–32 to 31–0.

Added

Section 14.2.4, “Chip Configuration Signals

.”

Added

.

Added “Unlike the MCF5272, the MCF5282 does not have an independent SDRAM clock signal. For the

MCF5282, the timing of the SDRAM controller is controlled by the CLKOUT signal.”

Added

Section 15.2.3.2, “SDRAM Byte Strobe Connections

.”

Added “Note: Because the MCF5282 has 24 external address lines, the maximum SDRAM address size

is 128 Mbits.”

Changed reset value to 0010_0000_0000_0000.

”

Changed “PSTCLK” references to “CLKOUT.”

Changed “TEA” to “TA.”

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3