Table 33-21, Lists mii – Motorola ColdFire MCF5281 User Manual

Page 706

Electrical Characteristics

33-22

Freescale Semiconductor

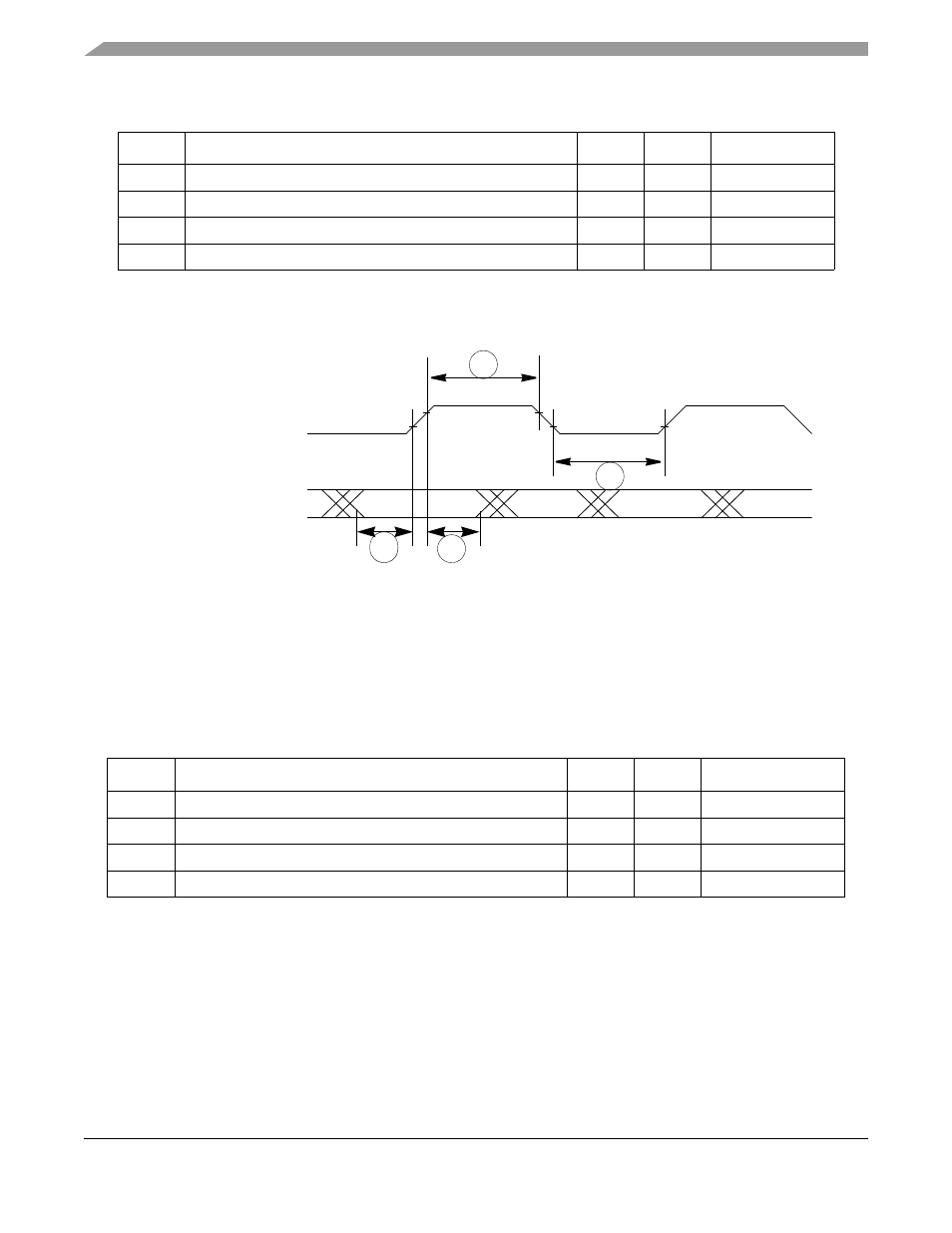

shows MII receive signal timings listed in

.

Figure 33-11. MII Receive Signal Timing Diagram

33.13.2 MII Transmit Signal Timing (ETXD[3:0], ETXEN, ETXER, ETXCLK)

The transmitter functions correctly up to a ETXCLK maximum frequency of 25 MHz +1%. In addition,

the processor clock frequency must exceed twice the ETXCLK frequency.

lists MII transmit channel timings.

shows MII transmit signal timings listed in

.

Table 33-21. MII Receive Signal Timing

Num

Characteristic

1

1

ERXDV, ERXCLK, and ERXD[0] have same timing in 10 Mbps 7-wire interface mode.

Min

Max

Unit

M1

ERXD[3:0], ERXDV, ERXER to ERXCLK setup

5

—

ns

M2

ERXCLK to ERXD[3:0], ERXDV, ERXER hold

5

—

ns

M3

ERXCLK pulse width high

35%

65%

ERXCLK period

M4

ERXCLK pulse width low

35%

65%

ERXCLK period

Table 33-22. MII Transmit Signal Timing

Num

Characteristic

1

1

ETXCLK, ETXD0, and ETXEN have the same timing in 10 Mbit 7-wire interface mode.

Min

Max

Unit

M5

ETXCLK to ETXD[3:0], ETXEN, ETXER invalid

5

—

ns

M6

ETXCLK to ETXD[3:0], ETXEN, ETXER valid

—

25

ns

M7

ETXCLK pulse width high

35%

65%

ETXCLK period

M8

ETXCLK pulse width low

35%

65%

ETXCLK period

M1

M2

ERXCLK (input)

ERXD[3:0] (inputs)

ERXDV

ERXER

M3

M4

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3