4 functional description, 1 transmitter/receiver clock source, 13uart output port command registers (uop1 n – Motorola ColdFire MCF5281 User Manual

Page 436: 4 functional description -16, 1 transmitter/receiver clock source -16, Section 23.4.1, “transmitter/receiver, Clock source, The tran

UART Modules

23-16

Freescale Semiconductor

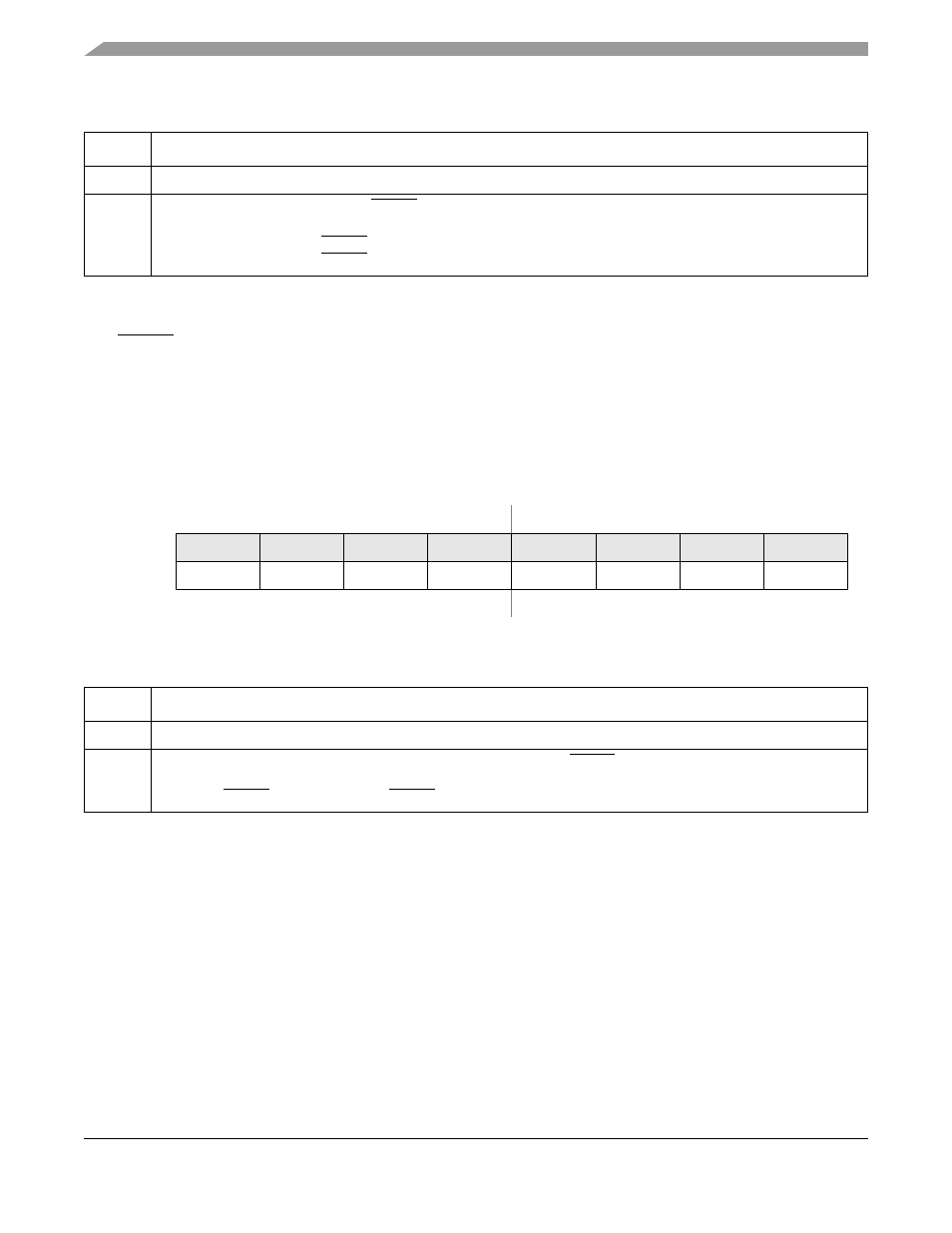

23.3.13 UART Output Port Command Registers (UOP1n/UOP0n)

The URTSn output can be asserted by writing a 1 to UOP1n[RTS] and negated by writing a 1 to

UOP0n[RTS].

23.4

Functional Description

This section describes operation of the clock source generator, transmitter, and receiver.

23.4.1

Transmitter/Receiver Clock Source

The internal bus clock serves as the basic timing reference for the clock source generator logic, which

consists of a clock generator and a programmable 16-bit divider dedicated to each UART. The 16-bit

divider is used to produce standard UART baud rates.

Table 23-11. UIPn Field Descriptions

Field

Description

7–1

Reserved

0

CTS

Current state of clear-to-send. The UCTSn value is latched and reflects the state of the input pin when UIPn is read.

Note: This bit has the same function and value as UIPCRn[CTS].

0 The current state of the UCTSn input is logic 0.

1 The current state of the UCTSn input is logic 1.

IPSBAR

Offset:

0x00_0238 (UOP10)

0x00_023C (UOP00)

0x00_0278 (UOP11)

0x00_027C (UOP01)

0x00_02B8 (UOP12)

0x00_02BC (UOP02)

Access: User write-only

7

6

5

4

3

2

1

0

R

W

0

0

0

0

0

0

0

RTS

Reset:

0

0

0

0

0

0

0

0

Figure 23-16. UART Output Port Command Registers (UOP1n/UOP0n)

Table 23-12. UOP1n/UOP0n Field Descriptions

Field

Description

7–1

Reserved, must be cleared.

0

RTS

Output port output. Controls assertion (UOP1)/negation (UOP0) of URTSn output.

0 Not affected.

1 Asserts URTSn in UOP1. Negates URTSn in UOP0.

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3