Figure 17-1 – Motorola ColdFire MCF5281 User Manual

Page 312

Fast Ethernet Controller (FEC)

17-2

Freescale Semiconductor

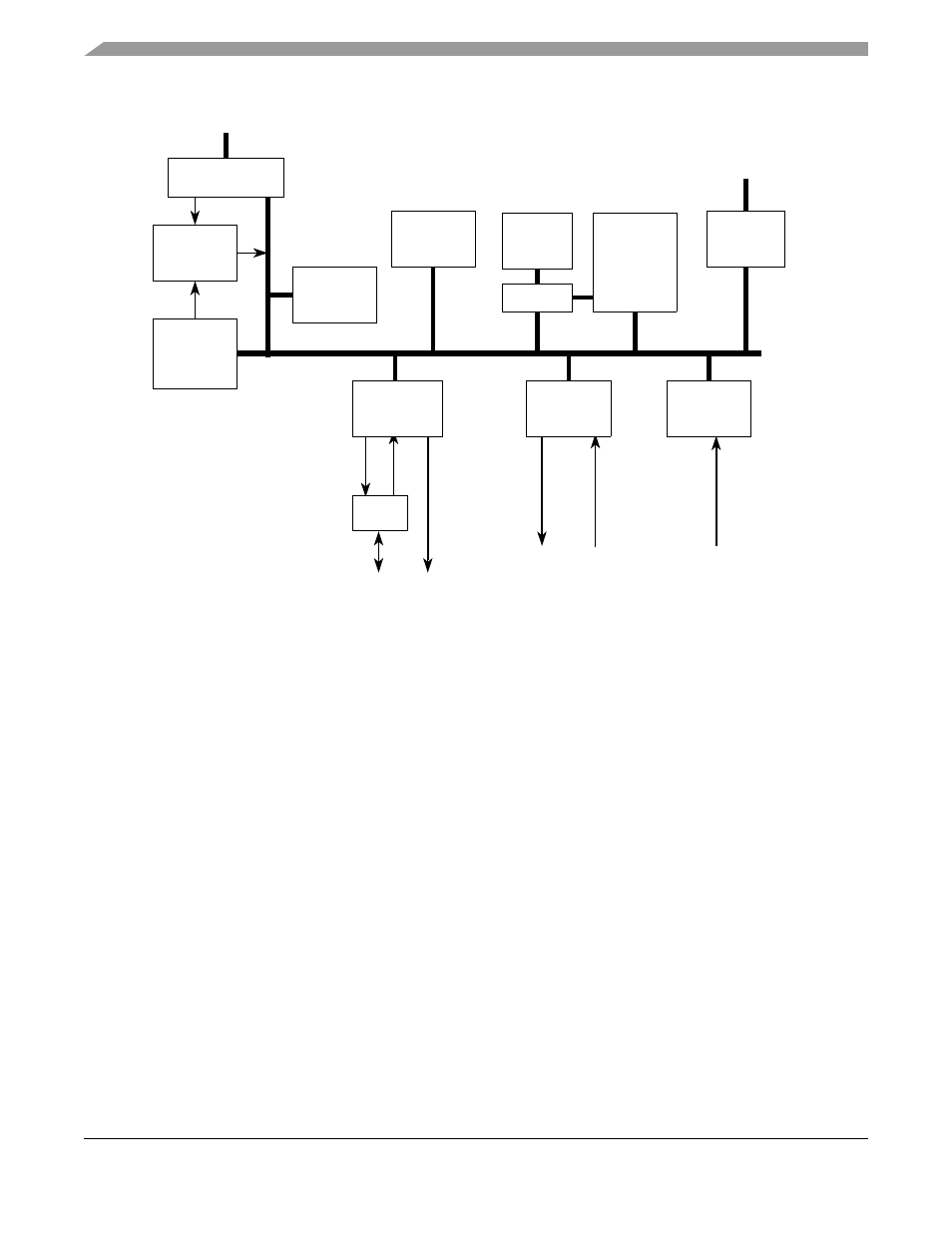

Figure 17-1. FEC Block Diagram

The descriptor controller is a RISC-based controller providing these functions in the FEC:

•

Initialization (those internal registers not initialized by you or hardware)

•

High level control of the DMA channels (initiating DMA transfers)

•

Interpreting buffer descriptors

•

Address recognition for receive frames

•

Random number generation for transmit collision backoff timer

NOTE

DMA references in this section refer to the FEC’s DMA engine. This DMA

engine transfers FEC data only and is not related to the eDMA controller

described in

Chapter 16, “DMA Controller Module

”

nor to the DMA timers

described in

Chapter 21, “DMA Timers (DTIM0–DTIM3).”

The RAM is the focal point of all data flow in the Fast Ethernet controller and divides into transmit and

receive FIFOs. The FIFO boundaries are programmable using the FRSR register. User data flows to/from

the DMA block from/to the receive/transmit FIFOs. Transmit data flows from the transmit FIFO into the

transmit block, and receive data flows from the receive block into the receive FIFO.

FIFO

FEC DMA

MII

Receive

Transmit

Controller

I/O

PAD

MDO

MDEN

MDI

MII/7-Wire data

FIFO

RAM

FEC Bus

option

FEC_TXEN

FEC_TXD[3:0]

FEC_TXER

FEC_TXCLK

FEC_CRS

FEC_COL

FEC_RXCLK

FEC_RXDV

FEC_RXD[3:0]

FEC_RXER

FEC_MDC

FEC_MDIO

RAM

Internal Bus

Control/Status

Descriptor

Controller

Bus

Controller

(RISC +

microcode)

Registers

Interface

Internal Bus

Crossbar Switch

Master Bus

Interface

MIB

Counter RAM

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3