2 memory map/register definition, 1 dma timer mode registers (dtmrn), 2 memory map/register definition -3 – Motorola ColdFire MCF5281 User Manual

Page 395: 1 dma timer mode registers (dtmr, 1 dma timer mode registers (dtmr n )

DMA Timers (DTIM0–DTIM3)

Freescale Semiconductor

21-3

21.2

Memory Map/Register Definition

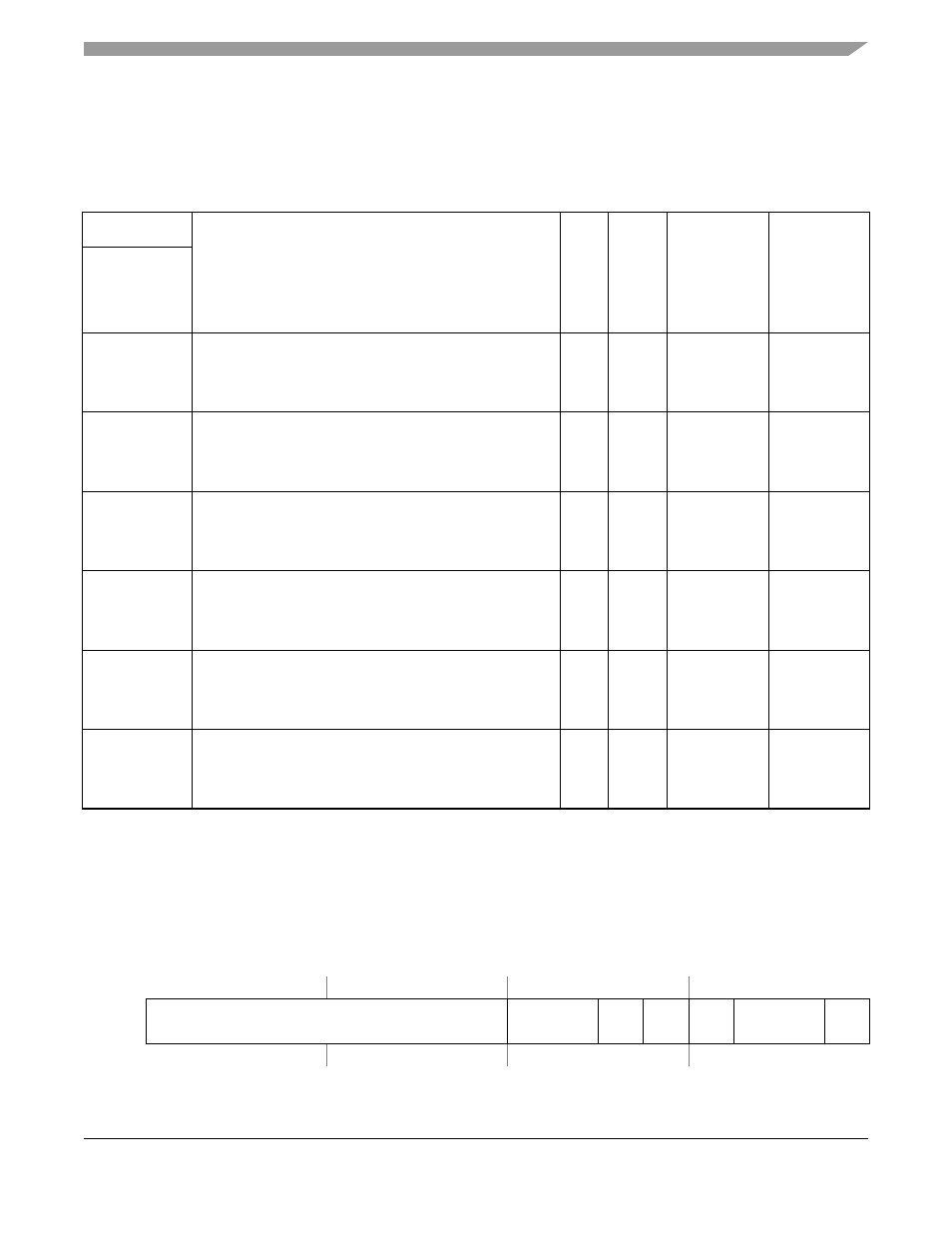

The timer module registers, shown in

, can be modified at any time.

21.2.1

DMA Timer Mode Registers (DTMRn)

The DTMRn registers program the prescaler and various timer modes.

Table 21-1. DMA Timer Module Memory Map

IPSBAR Offset

Register

Width

(bits)

Access

Reset Value

Section/Page

DMA Timer 0

DMA Timer 1

DMA Timer 2

DMA Timer 3

0x00_0400

0x00_0440

0x00_0480

0x00_04C0

DMA Timer n Mode Register (DTMRn)

16

R/W

0x0000

0x00_0402

0x00_0442

0x00_0482

0x00_04C2

DMA Timer n Extended Mode Register (DTXMRn) 8

R/W

0x00

0x00_0403

0x00_0443

0x00_0483

0x00_04C3

DMA Timer n Event Register (DTERn)

8

R/W

0x00

0x00_0404

0x00_0444

0x00_0484

0x00_04C4

DMA Timer n Reference Register (DTRRn)

32

R/W

0xFFFF_FFFF

0x00_0408

0x00_0448

0x00_0488

0x00_04C8

DMA Timer n Capture Register (DTCRn)

32

R/W

0x0000_0000

0x00_040C

0x00_044C

0x00_048C

0x00_04CC

DMA Timer n Counter Register (DTCNn)

32

R

0x0000_0000

IPSBAR

Offset:

0x00_0400 (DTMR0)

0x00_0440 (DTMR1)

0x00_0480 (DTMR2)

0x00_04C0 (DTMR3)

Access: User read/write

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

PS

CE

OM

ORRI

FRR

CLK

RST

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Figure 21-2. DTMRn Registers

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3