5 memory map and registers, 1 programming model, 2 memory map – Motorola ColdFire MCF5281 User Manual

Page 531: 5 memory map and registers -3, 1 programming model -3 27.5.2 memory map -3

Chip Configuration Module (CCM)

Freescale Semiconductor

27-3

27.4.3

D[26:24, 21, 19:16] (Reset Configuration Override)

If the external RCON pin is asserted during reset, then the states of these data pins during reset determine

the chip mode of operation, boot device, clock mode, and certain module configurations after reset.

27.5

Memory Map and Registers

This subsection provides a description of the memory map and registers.

27.5.1

Programming Model

The CCM programming model consists of these registers:

•

The chip configuration register (CCR) controls the main chip configuration.

•

The reset configuration register (RCON) indicates the default chip configuration.

•

The chip identification register (CIR) contains a unique part number.

Some control register bits are implemented as write-once bits. These bits are always readable, but once the

bit has been written, additional writes have no effect, except during debug and test operations.

Some write-once bits can be read and written while in debug mode. When debug mode is exited, the chip

configuration module resumes operation based on the current register values. If a write to a write-once

register bit occurs while in debug mode, the register bit remains writable on exit from debug or test mode.

shows the accessibility of write-once bits.

27.5.2

Memory Map

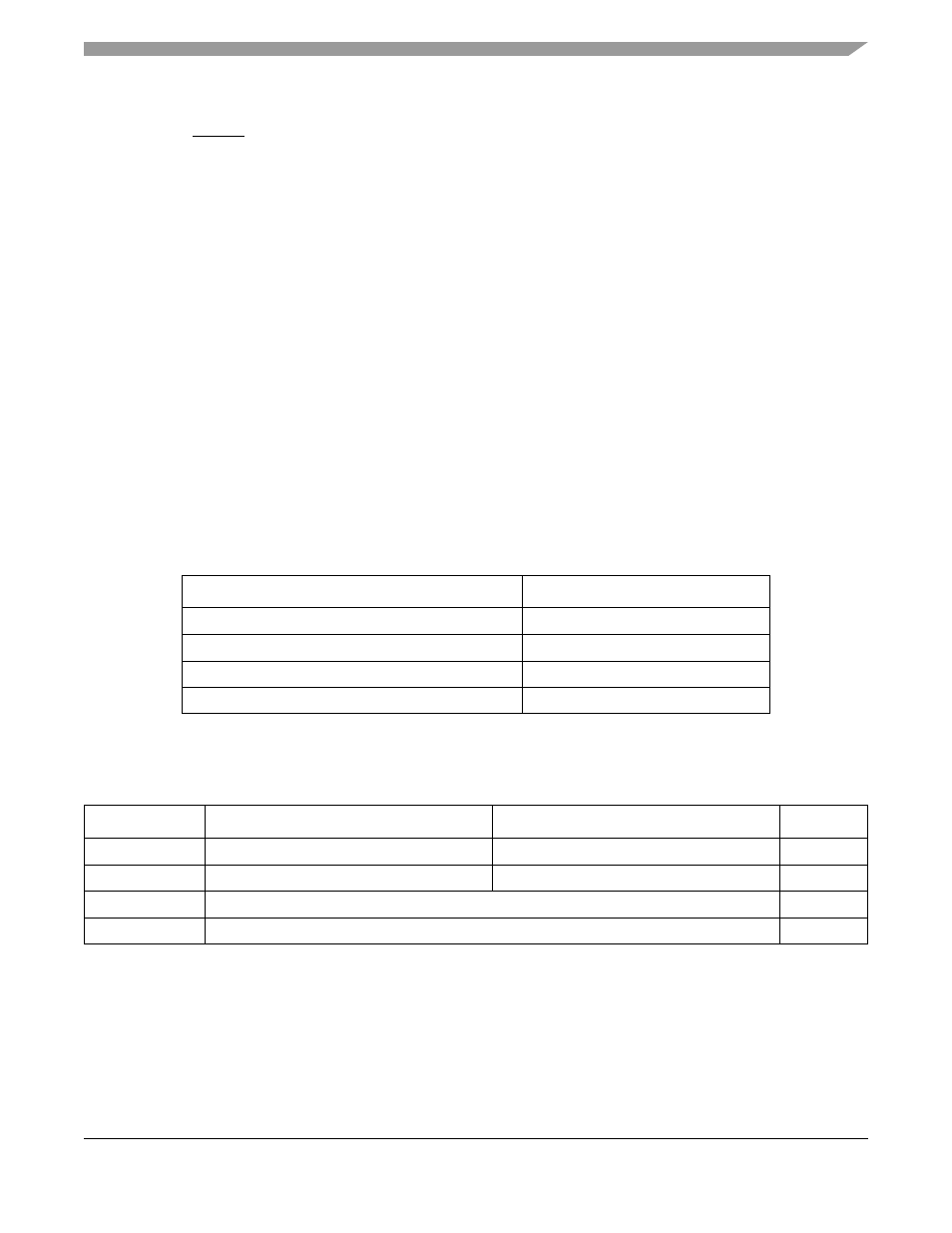

Table 27-2. Write-Once Bits Read/Write Accessibility

Configuration

Read/Write Access

All configurations

Read-always

Debug operation (all modes)

Write-always

Master mode

Write-once

Single-chip mode

Write-once

Table 27-3. Chip Configuration Module Memory Map

IPSBAR Offset

Bits 31–16

Bits 15–0

Access

1

1

S = CPU supervisor mode access only. User mode accesses to supervisor only addresses have no effect and result in a cycle

termination transfer error.

0x0011_0004

Chip Configuration Register (CCR)

Low-Power Control Register (LPCR)

2

2

,” for a description of the LPCR. It is shown here only to warn against accidental writes to

this register.

S

0x0011_0008

Reset Configuration Register (RCON)

Chip Identification Register (CIR)

S

0x0011_000c

Reserved

3

3

Writing to reserved addresses with values other than 0 could put the device in a test mode; reading returns 0s.

S

0x0011_0010

Unimplemented

4

—

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3