2 gpt compare force register (gpcforc), 3 gpt output compare 3 mask register (gptoc3m) – Motorola ColdFire MCF5281 User Manual

Page 374

General Purpose Timer Modules (GPTA and GPTB)

20-6

Freescale Semiconductor

20.5.2

GPT Compare Force Register (GPCFORC)

NOTE

A successful channel 3 output compare overrides any compare on channels

2:0. For each OC3M bit that is set, the output compare action reflects the

corresponding OC3D bit.

20.5.3

GPT Output Compare 3 Mask Register (GPTOC3M)

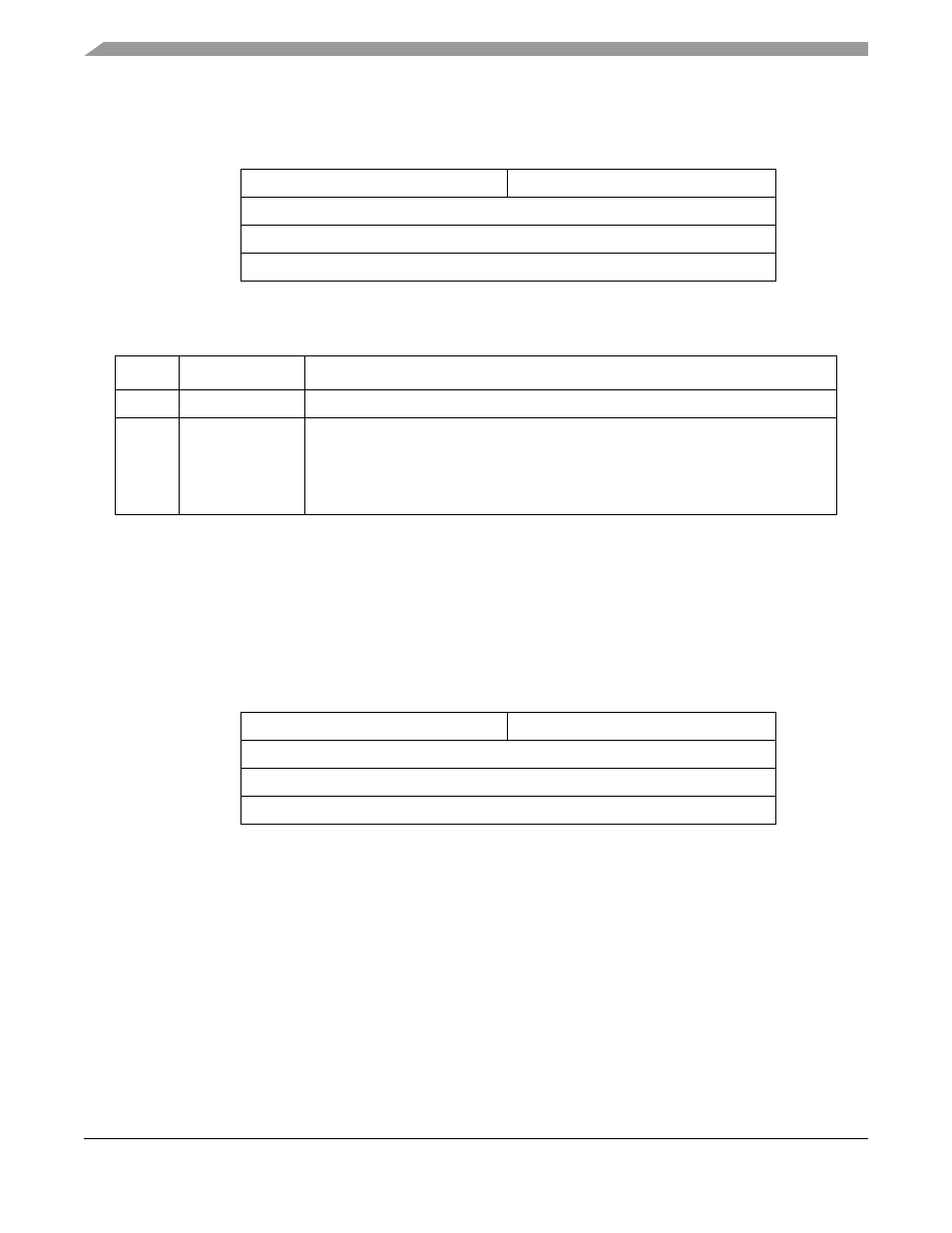

7

4

3

0

Field

—

FOC

Reset

0000_0000

R/W

R/W

Address

IPSBAR + 0x1A_00001, 0x1B_0001

Figure 20-3. GPT Input Compare Force Register (GPCFORC)

Table 20-5. GPTCFORC Field Descriptions

Bit(s)

Name

Description

7–4

—

Reserved, should be cleared.

3–0

FOC

Force output compare.Setting an FOC bit causes an immediate output compare on

the corresponding channel. Forcing an output compare does not set the output

compare flag. These bits are read anytime, write anytime.

1 Force output compare

0 No effect

7

4

3

0

Field

—

OC3M

Reset

0000_0000

R/W

R/W

Address

IPSBAR + 0x1A_0002, 0x1B_0002

Figure 20-4. GPT Output Compare 3 Mask Register (GPTOC3M)

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3