Motorola ColdFire MCF5281 User Manual

Page 251

Signal Descriptions

Freescale Semiconductor

14-11

TEST

Reserved, should be connected to VSS.

I

TCK

JTAG test logic clock.

I

TIP

Asserted to indicate that a bus transfer is in progress. Negated

during idle bus cycles.

O

TS

Asserted during the first CLKOUT cycle of a transfer when

address and attributes are valid.

O

UCTS[1:0]

Signals UART that it can begin data transmission.

I

URTS[1:0]

Automatic UART request to send outputs.

O

URXD[2:0]

Receiver serial data inputs.

I

UTXD[2:0]

Transmitter serial data outputs.

O

XTAL

Internal oscillator connection to the external crystal.

O

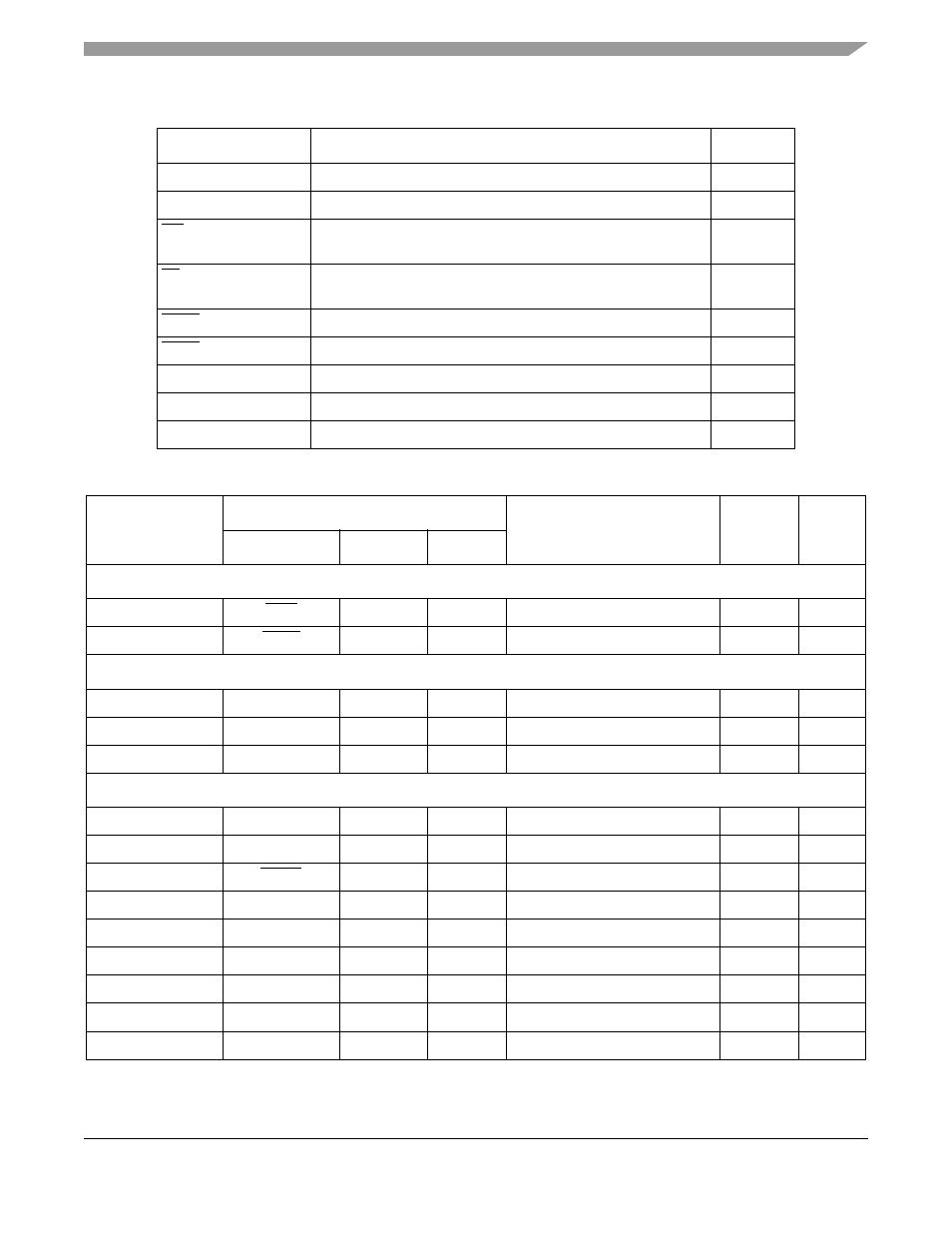

Table 14-3. MCF5282 Signals and Pin Numbers Sorted by Function

MAPBGA Pin

Pin Functions

Description

Primary

I/O

Internal

Pull-up

1

Primary

2

Secondary

Tertiary

Reset

R11

RSTI

—

—

Reset in

I

Yes

P11

RSTO

—

—

Reset out

O

—

Clock

T8

EXTAL

—

—

External clock/crystal in

I

—

R8

XTAL

—

—

Crystal drive

O

—

N7

CLKOUT

—

—

Clock out

O

—

Chip Configuration/Mode Selection

R14

CLKMOD0

—

—

Clock mode select

I

Yes

T14

CLKMOD1

—

—

Clock mode select

I

Yes

T11

RCON

—

—

Reset configuration enable

I

Yes

H1

D26

PA2

—

Chip mode

I/O

—

K2

D17

PB1

—

Chip mode

I/O

—

K3

D16

PB0

—

Chip mode

I/O

—

J4

D19

PB3

—

Boot device/data port size

I/O

—

K1

D18

PB2

—

Boot device/data port size

I/O

—

J2

D21

PB5

—

Output pad drive strength

I/O

—

Table 14-2. MCF5282 Alphabetical Signal Index (continued)

Abbreviation

Function

I/O

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3