3 qadc control register 2 (qacr2), 3 qadc control register 2 (qacr2) -14 – Motorola ColdFire MCF5281 User Manual

Page 552

Queued Analog-to-Digital Converter (QADC)

28-14

Freescale Semiconductor

28.6.5.3

QADC Control Register 2 (QACR2)

QACR2 is the mode control register for queue 2. This register governs queue operating mode and the use

of completion and/or pause interrupts. Typically, these bits are written once when the QADC is initialized

and not changed thereafter.

QACR2 also includes a resume feature that selects the resumption point for queue 2 after its operation is

suspended by a queue 1 trigger event. The primary reason for selecting re-execution of the entire queue or

subqueue is to guarantee that all samples are taken consecutively in one scan (coherency).

When subqueues are not used, queue 2 execution restarts after suspension with the first CCW in queue 2.

When a pause has previously occurred in queue 2 execution, queue execution restarts after suspension with

the first CCW in the current subqueue.

A subqueue is considered to be a stand-alone sequence of conversions. Once a pause flag has been set to

report subqueue completion, that subqueue is not repeated until all CCWs in queue 2 are executed.

For example, the RESUME bit can be used when the frequency of queue 1 trigger events prohibit queue

2 completion. If the rate of queue 1 execution is too high, it is best for queue 2 execution to continue with

the CCW that was being converted when queue 2 was suspended. This allows queue 2 to eventually

complete execution.

The beginning of queue 2 is defined by programming the BQ2 field in QACR2. BQ2 is usually set before

or at the same time as the queue operating mode for queue 2 is selected. If BQ2[6:0]

≥ 64, queue 2 has no

entries, the entire CCW table is dedicated to queue 1, and CCW63 is the end-of-queue 1. If BQ2[6:0] is 0,

the entire CCW table is dedicated to queue 2. A special case occurs when an operating mode is selected

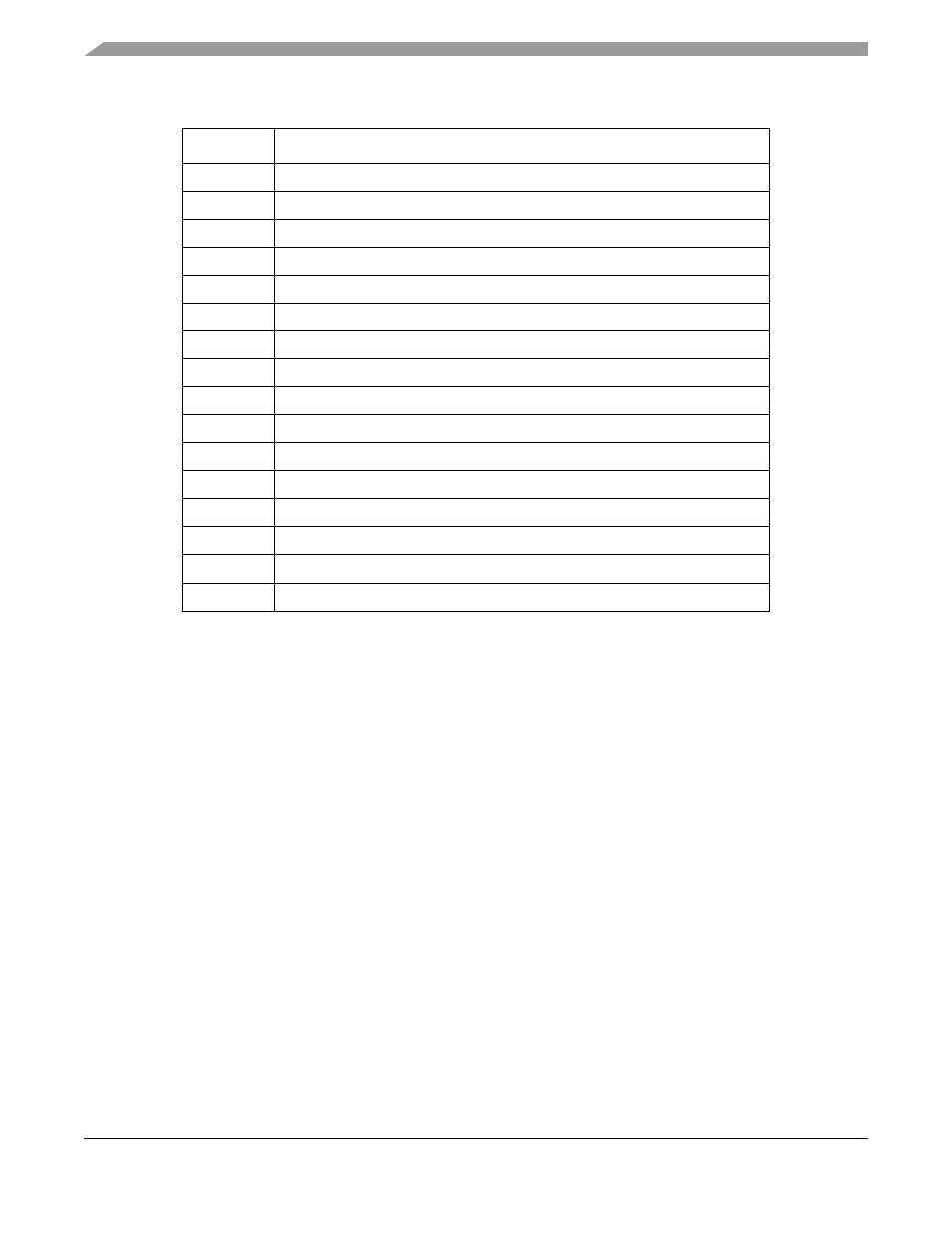

10000

Reserved mode

10001

Software-triggered continuous-scan mode

10010

External-trigger rising-edge continuous-scan mode

10011

External-trigger falling-edge continuous-scan mode

10100

Periodic timer continuous-scan mode: time = QCLK period

×

2

7

10101

Periodic timer continuous-scan mode: time = QCLK period

×

2

8

10110

Periodic timer continuous-scan mode: time = QCLK period

×

2

9

10111

Periodic timer continuous-scan mode: time = QCLK period

×

2

10

11000

Periodic timer continuous-scan mode: time = QCLK period

×

2

11

11001

Periodic timer continuous-scan mode: time = QCLK period

×

2

12

11010

Periodic timer continuous-scan mode: time = QCLK period

×

2

13

11011

Periodic timer continuous-scan mode: time = QCLK period

×

2

14

11100

Periodic timer continuous-scan mode: time = QCLK period

×

2

15

11101

Periodic timer continuous-scan mode: time = QCLK period

×

2

16

11110

Periodic timer continuous-scan mode: time = QCLK period

×

2

17

11111

Externally gated continuous-scan mode

Table 28-7. Queue 1 Operating Modes (continued)

MQ1[12:8]

Operating Mode

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3