Motorola ColdFire MCF5281 User Manual

Page 559

Queued Analog-to-Digital Converter (QADC)

Freescale Semiconductor

28-21

9–6

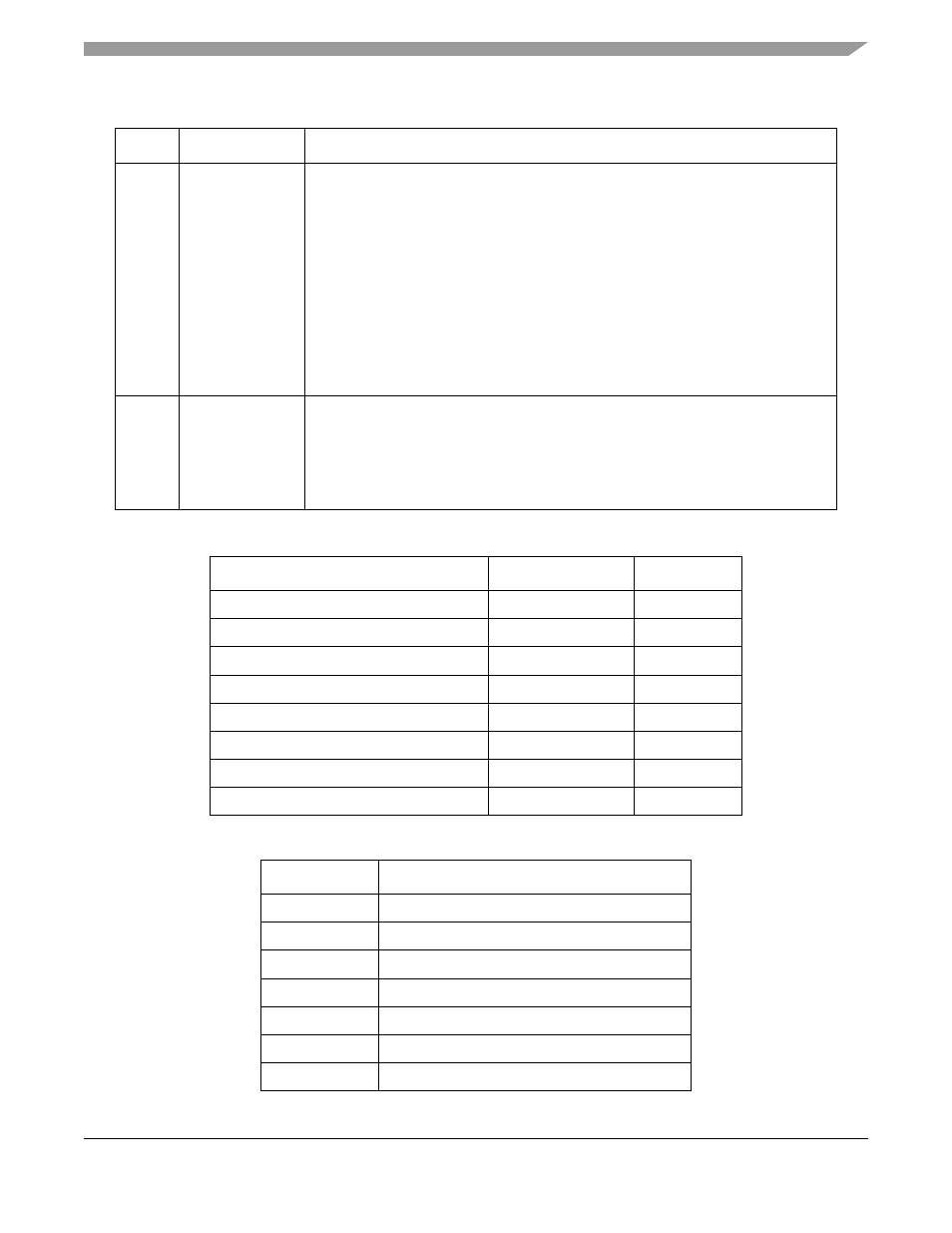

QS

Queue status. Indicates the current condition of queue 1 and queue 2. The two most

significant bits are associated primarily with queue 1, and the remaining two bits are

associated with queue 2. Because the priority scheme between the two queues

causes the status to be interlinked, the status bits must be considered as one 4-bit

field.

shows the bits in the QS field and how they denote the status of

queue 1 and queue 2.

The queue status field is affected by QADC stop mode. Because all of the analog logic

and control registers are reset, the queue status field is reset to queue 1 idle, queue

2 idle.

During debug mode, the queue status field is not modified. The queue status field

retains the status it held prior to freezing. As a result, the queue status can show

queue 1 active, queue 2 idle, even though neither queue is being executed during

freeze.

5–0

CWP

Command word pointer. Denotes which CCW is executing at present or was last

completed. CWP is a read-only field with a valid range of 0 to 63; write operations have

no effect.

During stop mode, CWP is reset to 0 because the control registers and the analog

logic are reset. When debug mode is entered, CWP is not changed; it points to the last

executed CCW.

Table 28-11. CCW Pause Bit Response

Scan Mode

Queue Operation

PF Asserts?

Externally triggered single-scan

Pauses

Yes

Externally triggered continuous-scan

Pauses

Yes

Interval timer trigger single-scan

Pauses

Yes

Interval timer continuous-scan

Pauses

Yes

Software-initiated single-scan

Continues

Yes

Software-initiated continuous-scan

Continues

Yes

Externally gated single-scan

Continues

No

Externally gated continuous-scan

Continues

No

Table 28-12. Queue Status

QS[9:6]

Queue 1/Queue 2 States

0000

Queue 1 idle, queue 2 idle

0001

Queue 1 idle, queue 2 paused

0010

Queue 1 idle, queue 2 active

0011

Queue 1 idle, queue 2 trigger pending

0100

Queue 1 paused, queue 2 idle

0101

Queue 1 paused, queue 2 paused

0110

Queue 1 paused, queue 2 active

Table 28-10. QASR0 Field Descriptions (continued)

Bit(s)

Name

Description

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3