9 uart auxiliary control register (uacrn), 9 uart auxiliary control register (uacr, 10uart interrupt status/mask registers (uisr n – Motorola ColdFire MCF5281 User Manual

Page 433: 9 uart auxiliary control register (uacr n ), The uacrs control the input enable

UART Modules

Freescale Semiconductor

23-13

23.3.9

UART Auxiliary Control Register (UACRn)

The UACRs control the input enable.

23.3.10 UART Interrupt Status/Mask Registers (UISRn/UIMRn)

The UISRs provide status for all potential interrupt sources. UISRn contents are masked by UIMRn. If

corresponding UISRn and UIMRn bits are set, internal interrupt output is asserted. If a UIMRn bit is

cleared, state of the corresponding UISRn bit has no effect on the output.

The UISRn and UIMRn registers share the same space in memory. Reading this register provides the user

with interrupt status, while writing controls the mask bits.

Table 23-8. UIPCRn Field Descriptions

Field

Description

7–5

Reserved

4

COS

Change of state (high-to-low or low-to-high transition).

0 No change-of-state since the CPU last read UIPCRn. Reading UIPCRn clears UISRn[COS].

1 A change-of-state longer than 25–50

μ

s occurred on the UCTSn input. UACRn can be programmed to generate

an interrupt to the CPU when a change of state is detected.

3–1

Reserved

0

CTS

Current state of clear-to-send. Starting two serial clock periods after reset, CTS reflects the state of UCTSn. If

UCTSn is detected asserted at that time, COS is set, which initiates an interrupt if UACRn[IEC] is enabled.

0 The current state of the UCTSn input is asserted.

1 The current state of the UCTSn input is deasserted.

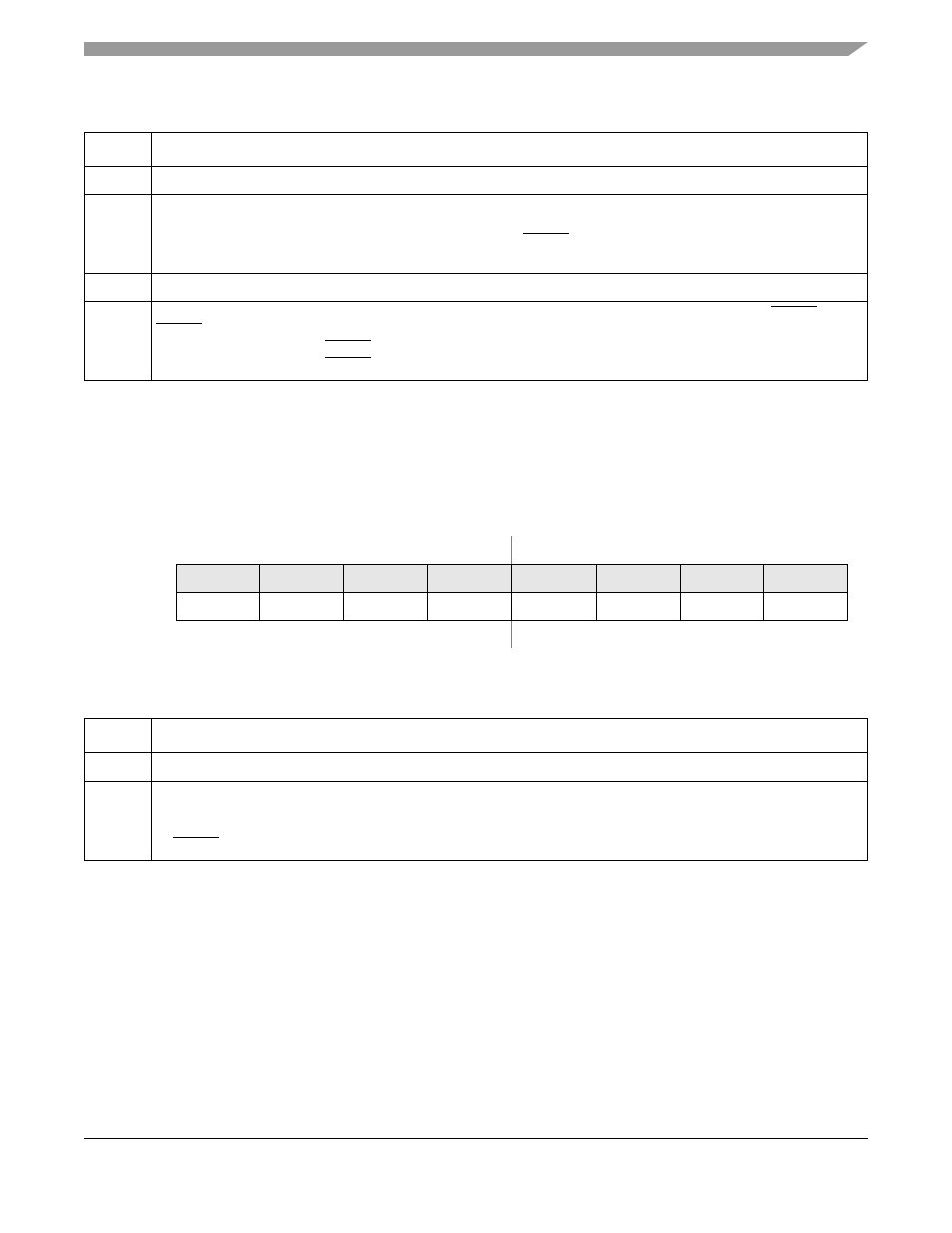

IPSBAR

Offset:

0x00_0210 (UACR0)

0x00_0250 (UACR1)

0x00_0290 (UACR2)

Access: User write-only

7

6

5

4

3

2

1

0

R

W

0

0

0

0

0

0

0

IEC

Reset:

0

0

0

0

0

0

0

0

Figure 23-11. UART Auxiliary Control Registers (UACRn)

Table 23-9. UACRn Field Descriptions

Field

Description

7–1

Reserved, must be cleared.

0

IEC

Input enable control.

0 Setting the corresponding UIPCRn bit has no effect on UISRn[COS].

1 UISRn[COS] is set and an interrupt is generated when the UIPCRn[COS] is set by an external transition on the

UCTSn input (if UIMRn[COS] = 1).

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3