3 register descriptions, 1 interrupt pending registers (iprhn, iprln), 3 register descriptions -6 – Motorola ColdFire MCF5281 User Manual

Page 196: 1 interrupt pending registers (iprhn, iprln) -6, 1 interrupt pending registers (iprh n , iprl n )

Interrupt Controller Modules

10-6

Freescale Semiconductor

10.3

Register Descriptions

10.3.1

Interrupt Pending Registers (IPRHn, IPRLn)

The IPRHn and IPRLn registers,

and

, are each 32 bits in size, and provide a bit

map for each interrupt request to indicate if there is an active request (1 = active request, 0 = no request)

for the given source. The state of the interrupt mask register does not affect the IPRn. The IPRn is cleared

by reset. The IPRn is a read-only register, so any attempted write to this register is ignored. Bit 0 is not

implemented and reads as a zero.

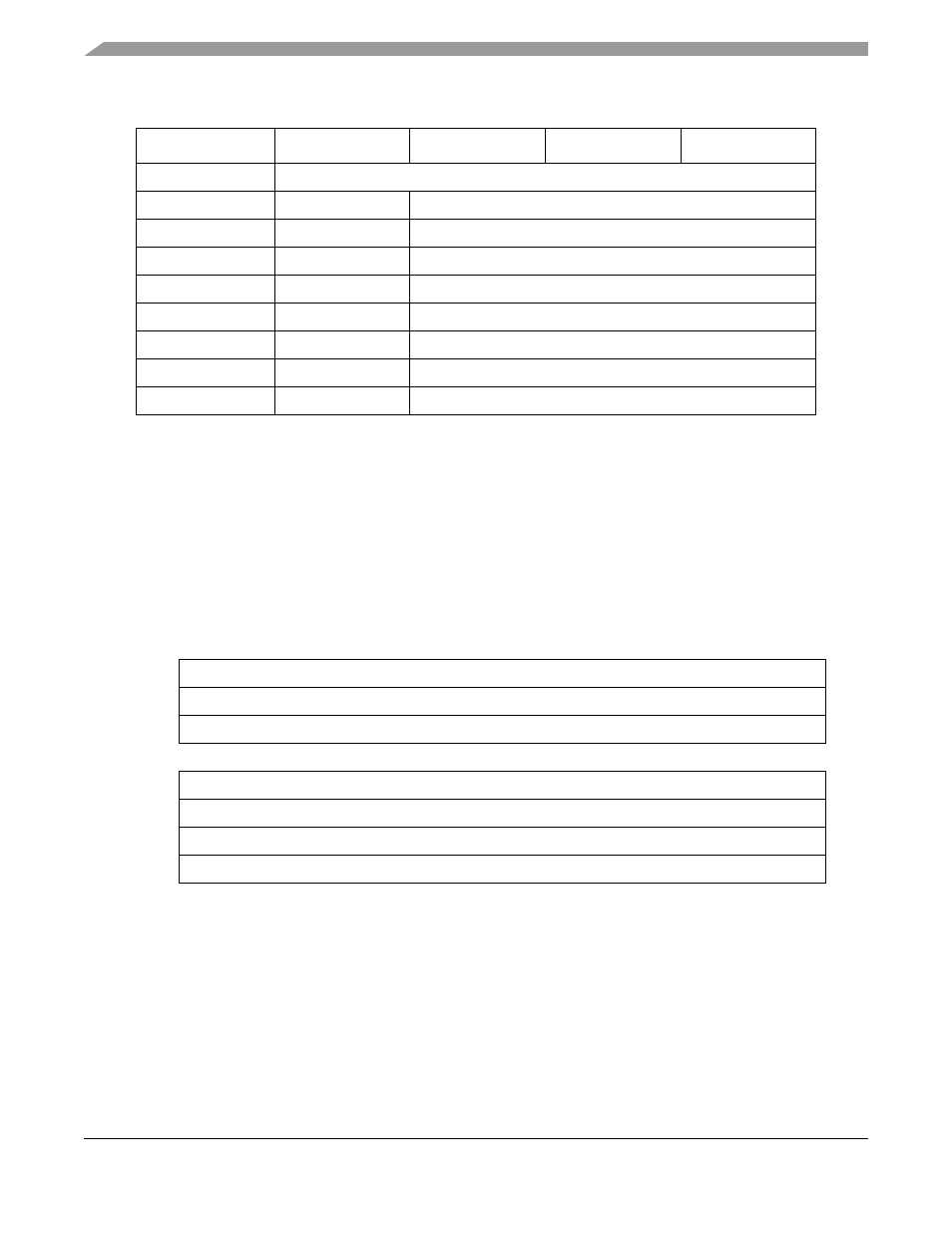

0x80–0xDC

Reserved

0xE0

SWIACK

Reserved

0xE4

L1IACK

Reserved

0xE8

L2IACK

Reserved

0xEC

L3IACK

Reserved

0xF0

L4IACK

Reserved

0xF4

L5IACK

Reserved

0xF8

L6IACK

Reserved

0xFC

L7IACK

Reserved

31

16

Field

INT[63:48]

Reset

0000_0000_0000_0000

R/W

R

15

0

Field

INT[47:32]

Reset

0000_0000_0000_0000

R/W

R

IPSBAR + 0xC00, 0xD00

Figure 10-1. Interrupt Pending Register High (IPRHn)

Table 10-3. Interrupt Controller Memory Map (continued)

Module Offset

Bits[31:24]

Bits[23:16]

Bits[15:8]

Bits[7:0]

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3