4 functional description, 1 overview, 2 port digital i/o timing – Motorola ColdFire MCF5281 User Manual

Page 527: 4 functional description -27, 1 overview -27 26.4.2 port digital i/o timing -27, Section 26.4, “functional description

General Purpose I/O Module

Freescale Semiconductor

26-27

26.4

Functional Description

26.4.1

Overview

The initial pin function is determined during reset configuration. The pin assignment registers allow the

user to select between digital I/O or another pin function after reset.

In single-chip mode, all pins are configured as digital I/O by default, except for debug data pins

(DDATA[3:0]) and processor status pins (PST[3:0]). These pins are configured for their primary functions

by default in all modes.

Every digital I/O pin is individually configurable as an input or an output via a data direction register

(DDRn).

Every port has an output data register (PORTn) and a pin data register (PORTnP/SETn) to monitor and

control the state of its pins. Data written to a PORTn register is stored and then driven to the corresponding

port n pins configured as outputs.

Reading a PORTn register returns the current state of the register regardless of the state of the

corresponding pins.

Reading a PORTnP/PSETn register returns the current state of the corresponding pins when configured as

digital I/O, regardless of whether the pins are inputs or outputs.

Every port has a PORTnP/SETn register and a clear register (CLRn) for setting or clearing individual bits

in the PORTn register.

In master mode, port A and B function as the upper external data bus, D[31:16]. When the PCDPA bit is

set, ports C and D function as the lower external data bus, D[15:0]. Ports E–J are configured to support

external memory functions.

The ports module does not generate interrupt requests.

26.4.2

Port Digital I/O Timing

Input data on all pins configured as digital I/O is synchronized to the rising edge of CLKOUT, as shown

in

2

PUAPA2

Port UA pin assignment 2. This bit configures the port UA2 pin for its primary function

(UTXD1) or digital I/O.

1 Port UA2 pin configured for primary function (UTXD1)

0 Port UA2 pin configured for digital I/O

1

PUAPA1

Port UA pin assignment 1. This bit configures the port UA1 pin for its primary function

(URXD0) or digital I/O.

1 Port UA1 pin configured for primary function (URXD0)

0 Port UA1 pin configured for digital I/O

0

PUAPA0

Port UA pin assignment 0. This bit configures the port UA0 pin for its primary function

(UTXD0) or digital I/O.

1 Port UA0 pin configured for primary function (UTXD0)

0 Port UA0 pin configured for digital I/O

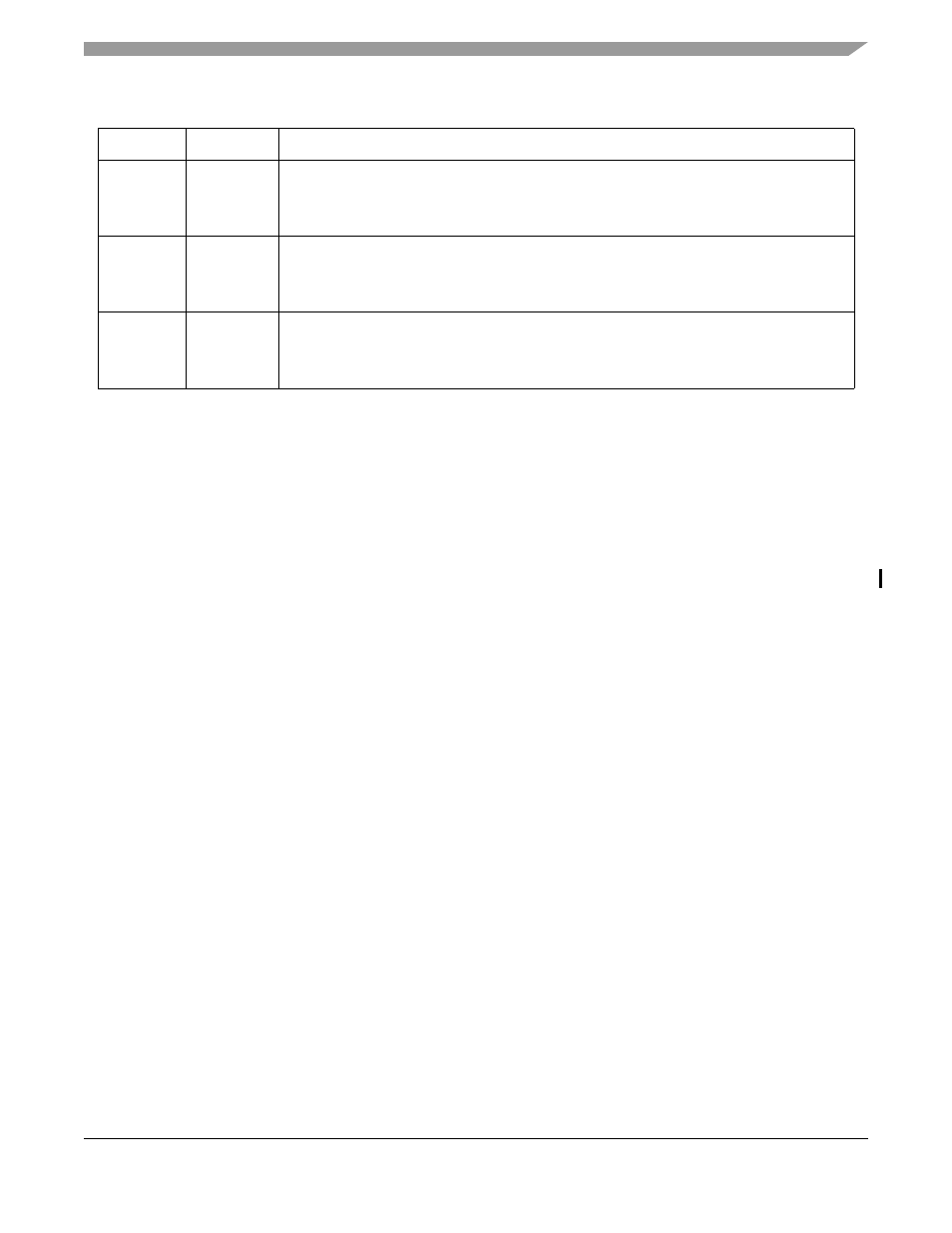

Table 26-19. PUAPAR Field Descriptions (continued)

Bits

Name

Description

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3