Motorola ColdFire MCF5281 User Manual

Page 662

Debug Support

30-44

Freescale Semiconductor

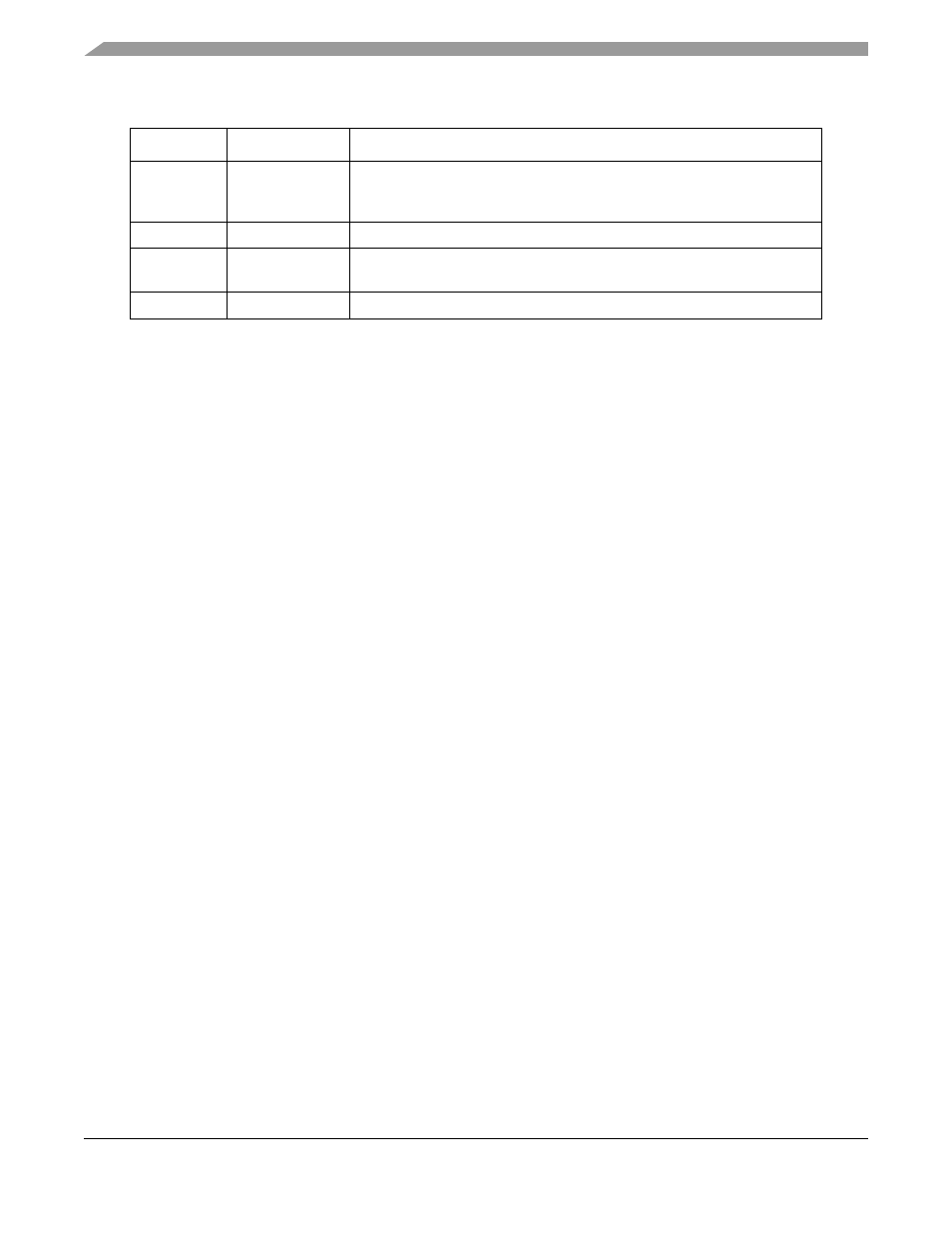

The move-to-SR, STLDSR, and RTE instructions include an optional PST = 0x3 value, indicating an entry

into user mode. Additionally, if the execution of a RTE instruction returns the processor to emulator mode,

a multiple-cycle status of 0xD is signaled.

Similar to the exception processing mode, the stopped state (PST = 0xE) and the halted state (PST = 0xF)

display this status throughout the entire time the ColdFire processor is in the given mode.

rte

PST = 0x7, {PST = 0xB, DD = source operand}, {PST = 3}, { PST =0xB,

DD =source operand},

PST = 0x5, {[PST = 0x9AB], DD = target address}

stldsr.w

#imm

PST = 0x1, {PST = 0xA, DD = destination operand, PST = 0x3}

stop

#imm

PST = 0x1,

PST = 0xE

wdebug

PST = 0x1, {PST = 0xB, DD = source, PST = 0xB, DD = source}

Table 30-24. PST/DDATA Specification for Supervisor-Mode Instructions

Instruction

Operand Syntax

PST/DDATA

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3