10 interrupts, 1 interrupt operation, 2 interrupt sources – Motorola ColdFire MCF5281 User Manual

Page 606: 10interrupts -68, Table 28-25, Illus

Queued Analog-to-Digital Converter (QADC)

28-68

Freescale Semiconductor

CAUTION

Leakage below 200 nA is obtainable only within a limited temperature

range.

28.10 Interrupts

The four interrupt lines are outputs of the module and have no priority or arbitration within the module.

28.10.1 Interrupt Operation

QADC inputs can be monitored by polling or by using interrupts. When interrupts are not needed, the

completion flag and the pause flag for each queue can be monitored in the status register (QASR0). In other

words, flag bits can be polled to determine when new results are available.

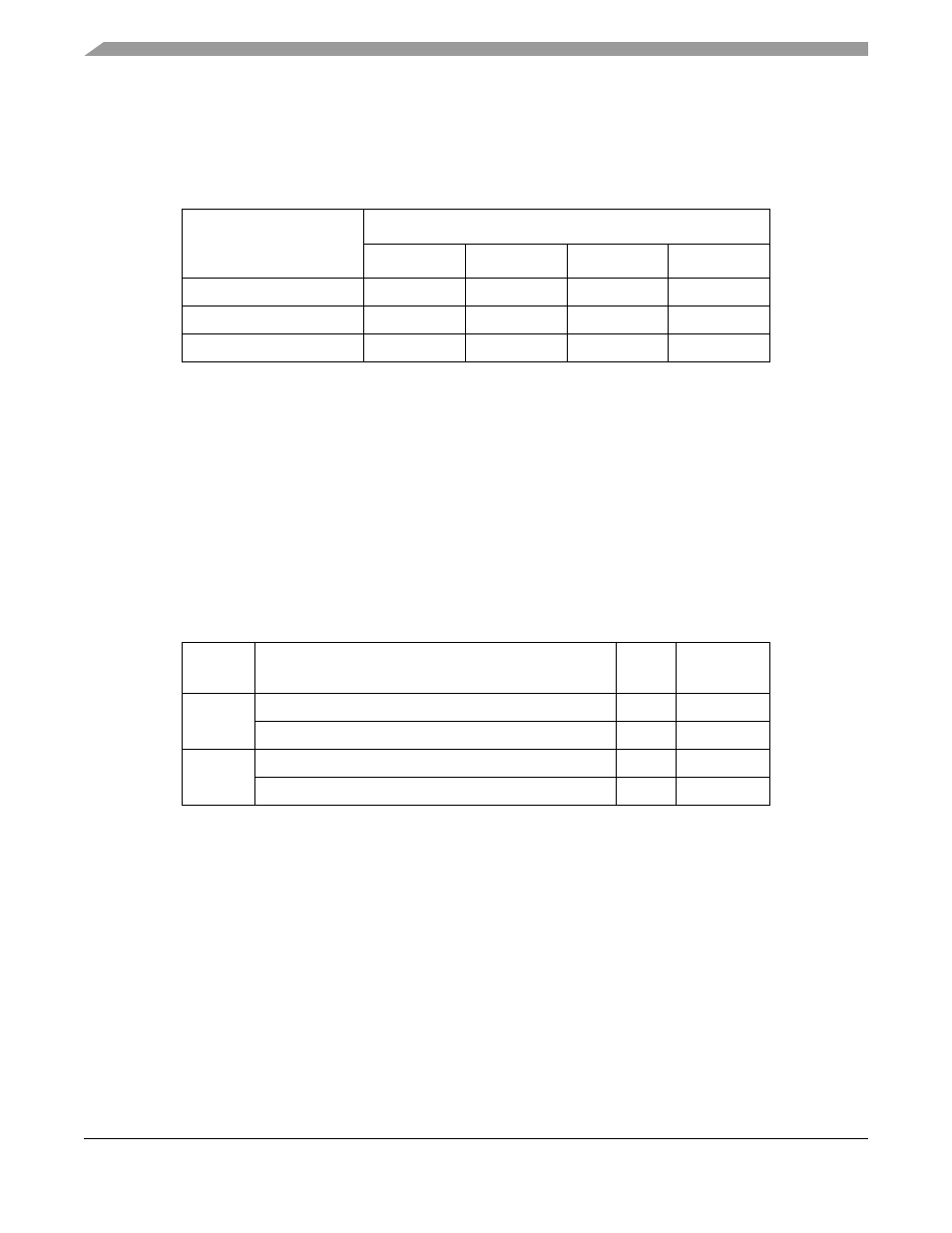

shows the status flag and interrupt enable bits which correspond to queue 1 and queue 2

activity.

If interrupts are enabled for an event, the QADC requests interrupt service when the event occurs. Using

interrupts does not require continuously polling the status flags to see if an event has taken place; however,

status flags must be cleared after an interrupt is serviced, in order to remove the interrupt request

In both polled and interrupt-driven operating modes, status flags must be re-enabled after an event occurs.

Flags are re-enabled by clearing the appropriate QASR0 bits in a particular sequence. QASR0 must first

be read, then 0s must be written to the flags that are to be cleared. If a new event occurs between the time

that the register is read and the time that it is written, the associated flag is not cleared.

28.10.2 Interrupt Sources

The QADC includes four sources of interrupt requests, each of which is separately enabled. Each time the

result is written for the last conversion command word (CCW) in a queue, the completion flag for the

corresponding queue is set, and when enabled, an interrupt is requested. In the same way, each time the

Table 28-25. Error Resulting from Input Leakage (I

Off

)

Source Impedance

Leakage Value (10-Bit Conversions)

100 nA

200 nA

500 nA

1000 nA

1 k

Ω

—

—

0.1 counts

0.2 counts

10 k

Ω

0.2 counts

0.4 counts

1 counts

2 counts

100 k

Ω

2 counts

4 count

10 counts

20 counts

Table 28-26. QADC Status Flags and Interrupt Sources

Queue

Queue Activity

Status

Flag

Interrupt

Enable Bit

Queue 1

Result written for last CCW in queue 1

CF1

CIE1

Result written for a CCW with pause bit set in queue 1

PF1

PIE1

Queue 2

Result written for last CCW in queue 2

CF2

CIE2

Result written for a CCW with pause bit set in queue 2

PF2

PIE2

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3