Table 30-8 describes csr fields – Motorola ColdFire MCF5281 User Manual

Page 629

Debug Support

Freescale Semiconductor

30-11

describes CSR fields.

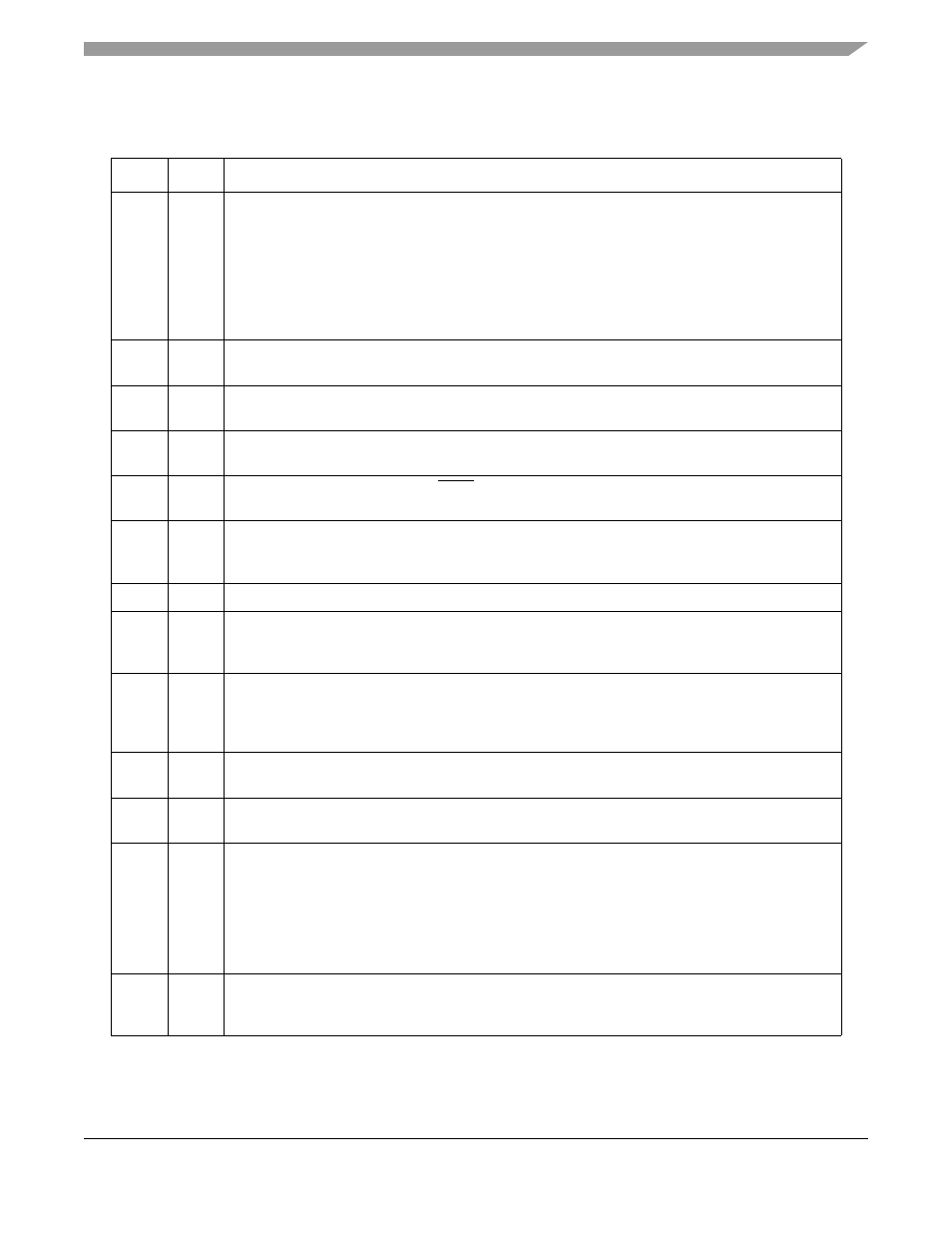

Table 30-8. CSR Field Descriptions

Bit

Name

Description

31–28

BSTAT Breakpoint status. Provides read-only status information concerning hardware breakpoints. BSTAT

is cleared by a TDR write or by a CSR read when either a level-2 breakpoint is triggered or a level-1

breakpoint is triggered and the level-2 breakpoint is disabled.

0000 No breakpoints enabled

0001 Waiting for level-1 breakpoint

0010 Level-1 breakpoint triggered

0101 Waiting for level-2 breakpoint

0110 Level-2 breakpoint triggered

27

FOF

Fault-on-fault. If FOF is set, a catastrophic halt occurred and forced entry into BDM. FOF is cleared

whenever CSR is read.

26

TRG

Hardware breakpoint trigger. If TRG is set, a hardware breakpoint halted the processor core and

forced entry into BDM. Reset, the debug

GO

command, or reading CSR will clear TRG.

25

HALT

Processor halt. If HALT is set, the processor executed a HALT and forced entry into BDM. Reset, the

debug

GO

command, or reading CSR will clear HALT.

24

BKPT

Breakpoint assert. If BKPT is set, BKPT was asserted, forcing the processor into BDM. Reset, the

debug

GO

command, or reading CSR will clear BKPT.

23–20

HRL

Hardware revision level. Indicates the level of debug module functionality. An emulator could use this

information to identify the level of functionality supported.

0000 Initial debug functionality (Revision A) (This is the only valid value for this device.)

19–17

—

Reserved, should be cleared.

16

IPW

Inhibit processor writes. Setting IPW inhibits processor-initiated writes to the debug module’s

programming model registers. IPW can be modified only by commands from the external

development system.

15

MAP

Force processor references in emulator mode.

0 All emulator-mode references are mapped into supervisor code and data spaces.

1 The processor maps all references while in emulator mode to a special address space, TT = 10,

TM = 101 or 110.

14

TRC

Force emulation mode on trace exception. If TRC = 1, the processor enters emulator mode when a

trace exception occurs. If TRC=0, the processor enters supervisor mode.

13

EMU

Force emulation mode. If EMU = 1, the processor begins executing in emulator mode. See

Section 30.6.1.1, “Emulator Mode

.”

12–11

DDC

Debug data control. Controls operand data capture for DDATA, which displays the number of bytes

defined by the operand reference size before the actual data; byte displays 8 bits, word displays 16

bits, and long displays 32 bits (one nibble at a time across multiple PSTCLK cycles). See

.

00 No operand data is displayed.

01 Capture all write data.

10 Capture all read data.

11 Capture all read and write data.

10

UHE

User halt enable. Selects the CPU privilege level required to execute the HALT instruction.

0 HALT is a supervisor-only instruction.

1 HALT is a supervisor/user instruction.

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3