2 synthesizer status register (synsr), 2 synthesizer status register (synsr) -8 – Motorola ColdFire MCF5281 User Manual

Page 178

Clock Module

9-8

Freescale Semiconductor

9.6.2.2

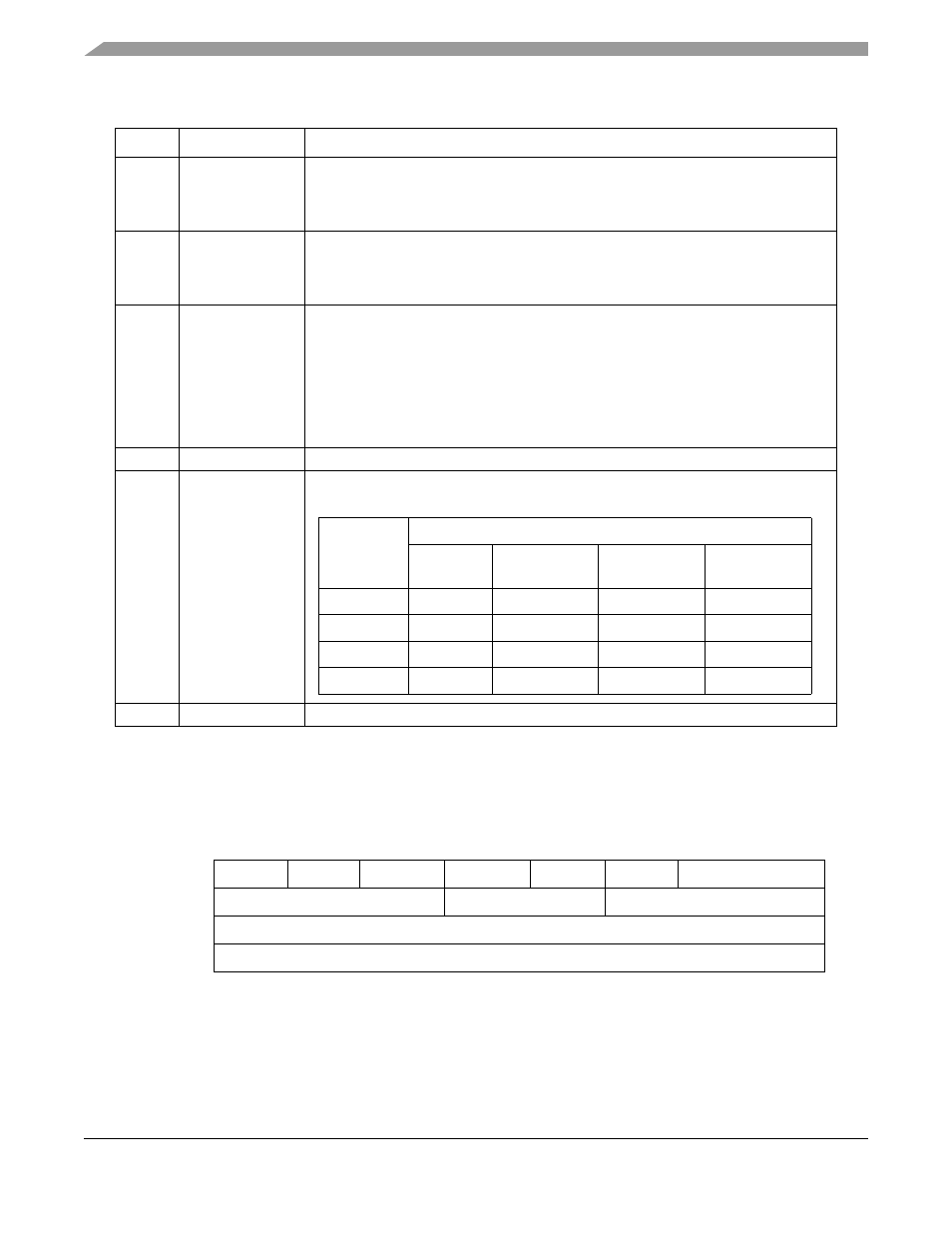

Synthesizer Status Register (SYNSR)

The SYNSR is a read-only register that can be read at any time. Writing to the SYNSR has no effect and

terminates the cycle normally.

7

LOCEN

Enables the loss-of-clock function. LOCEN does not affect the loss of lock function.

1 Loss-of-clock function enabled

0 Loss-of-clock function disabled

Note: In external clock mode, the LOCEN bit has no effect

.

6

DISCLK

Disable CLKOUT determines whether CLKOUT is driven. Setting the DISCLK bit

holds CLKOUT low.

1 CLKOUT disabled

0 CLKOUT enabled

5

FWKUP

Fast wakeup determines when the system clocks are enabled during wakeup from

stop mode.

1 System clocks enabled on wakeup regardless of PLL lock status

0 System clocks enabled only when PLL is locked or operating normally

Note: When FWKUP = 0, if the PLL or oscillator is enabled and unintentionally lost in

stop mode, the PLL wakes up in self-clocked mode or reference clock mode

depending on the clock that was lost. In external clock mode, the FWKUP bit has no

effect on the wakeup sequence.

4

—

Reserved, should be cleared.

3–2

STPMD

Control PLL and CLKOUT operation in stop mode. The following table illustrates

STPMD operation in stop mode.

1–0

—

Reserved, should be cleared.

7

6

5

4

3

2

1

0

Field PLLMODE

PLLSEL

PLLREF

LOCKS

LOCK

LOCS

—

Reset

See note 1

See note 2

000

R/W

R

Address

IPSBAR + 0x0012_0002

Note: 1. Reset state determined during reset configuration.

2. See the LOCKS and LOCK bit descriptions.

Figure 9-4. Synthesizer Status Register (SYNSR)

Table 9-4. SYNCR Field Descriptions (continued)

Bit(s)

Name

Description

STPMD[1:0]

Operation During Stop Mode

System

Clocks

PLL

OSC

CLKOUT

00

Disabled

Enabled

Enabled

Enabled

01

Disabled

Enabled

Enabled

Disabled

10

Disabled

Disabled

Enabled

Disabled

11

Disabled

Disabled

Disabled

Disabled

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3