2 qadc control register 1 (qacr1), 2 qadc control register 1 (qacr1) -12 – Motorola ColdFire MCF5281 User Manual

Page 550

Queued Analog-to-Digital Converter (QADC)

28-12

Freescale Semiconductor

28.6.5.2

QADC Control Register 1 (QACR1)

QACR1 is the mode control register for queue 1. This register governs queue operating mode and the use

of completion and/or pause interrupts. Typically, these bits are written once when the QADC is initialized

and are not changed thereafter.

Stop mode resets this register.

0010101

44

0110101

108

1010101

172

1110101

236

0010110

46

0110110

110

1010110

174

1110110

238

0010111

48

0110111

112

1010111

176

1110111

240

0011000

50

0111000

114

1011000

178

1111000

242

0011001

52

0111001

116

1011001

180

1111001

244

0011010

54

0111010

118

1011010

182

1111010

246

0011011

56

0111011

120

1011011

184

1111011

248

0011100

58

0111100

122

1011100

186

1111100

250

0011101

60

0111101

124

1011101

188

1111101

252

0011110

62

0111110

126

1011110

190

1111110

254

0011111

64

0111111

128

1011111

192

1111111

256

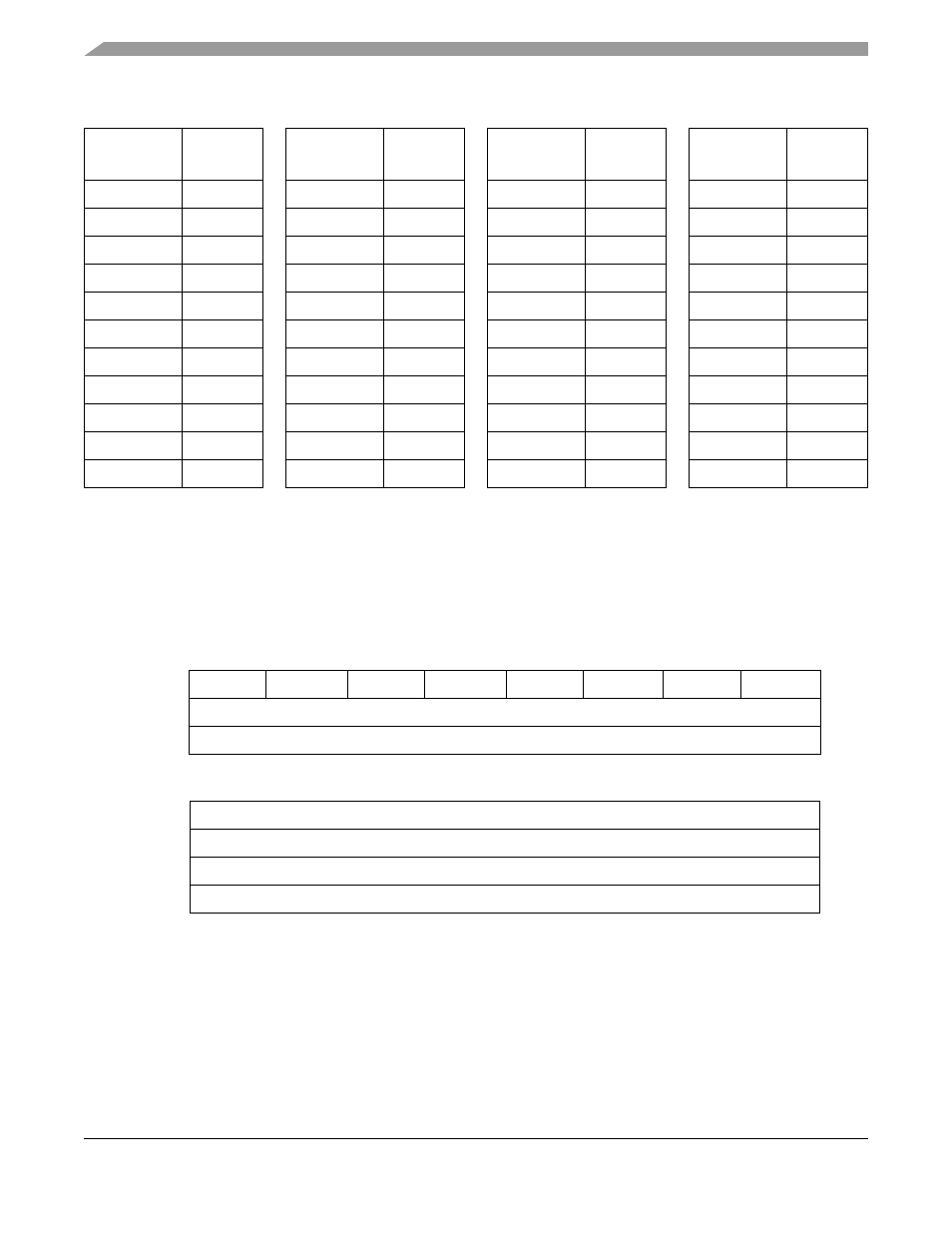

15

14

13

12

11

10

9

8

Field

CIE1

PIE1

SSE1

MQ112

MQ111

MQ110

MQ19

MQ18

Reset

0000_0000

R/W:

R/W

7

0

Field

—

Reset

0000_0000

R/W:

R

Address

IPSBAR + 0x19_000c, 0x19_000d

Figure 28-9. QADC Control Register 1 (QACR1)

Table 28-5. Prescaler f

SYS

Divide-by Values (continued)

QPR[6:0]

f

SYS

Divisor

QPR[6:0]

f

SYS

Divisor

QPR[6:0]

f

SYS

Divisor

QPR[6:0]

f

SYS

Divisor

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3