Motorola ColdFire MCF5281 User Manual

Page 731

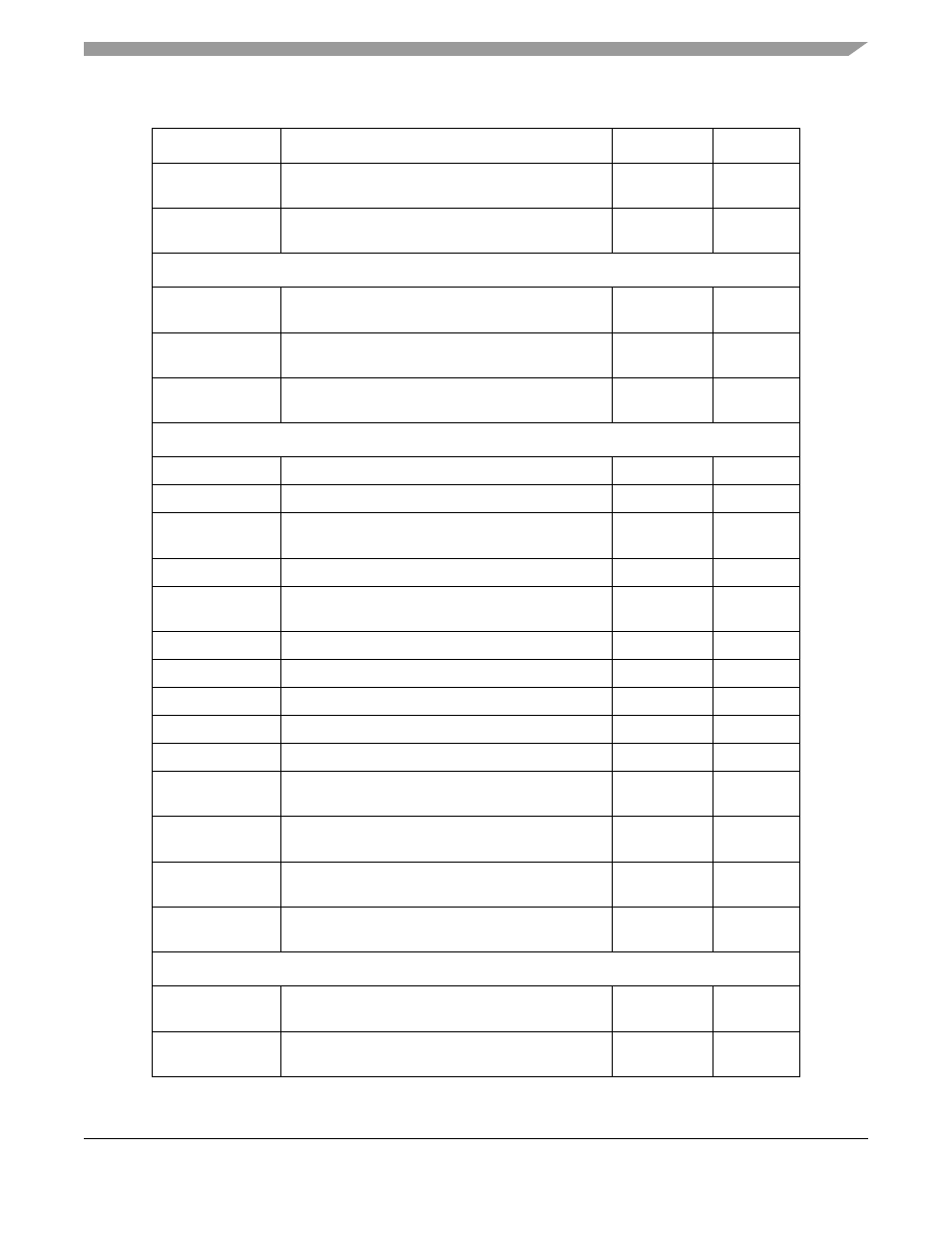

Register Memory Map

Freescale Semiconductor

A-19

IPSBAR +

0x17_0002

PIT Modulus Register 2

PMR 2

16

IPSBAR +

0x17_0004

PIT Count Register 2

PCNTR 2

16

Programmable Interrupt Timer 3 Registers

IPSBAR +

0x18_0000

PIT Control and Status Register 3

PCSR 3

16

IPSBAR +

0x18_0002

PIT Modulus Register 3

PMR 3

16

IPSBAR +

0x18_0004

PIT Count Register 3

PCNTR 3

16

QADC Registers

0x19_0000

QADC Module Configuration Register

QADCMCR

16

0x19_0006

Port QA Data Register

PORTQA

8

IPSBAR +

0x19_0007

Port QB Data Register

PORTQB

8

0x19_0008

Port QA Data Direction Register

DDRQA

8

IPSBAR +

0x19_0009

Port QB Data Direction Register

DDRQB

8

0x19_000A

QADC Control Register 0

QACR0

16

0x19_000C

QADC Control Register 1

QACR1

16

0x19_000E

QADC Control Register 2

QACR2

16

0x19_0010

QADC Status Register 0

QASR0

16

0x19_0012

QADC Status Register 1

QASR1

16

0x19_0200–

0x19_027E

Conversion Command Word Table

CCW0–

CCW63

64x16

0x19_0280–

0x19_02FE

Right Justified, Unsigned Result Register

RJURR0–

RJURR63

64x16

0x19_0300–

0x19_037E

Left Justified, Signed Result Register

LJSRR0–

LJSRR63

64x16

0x19_0380–

0x19_03FE

Left Justified, Unsigned Result Register

LJURR0–

LJURR63

64x16

General Purpose Timer A Registers

IPSBAR +

0x1A_0000

GPTA IC/OC Select Register

GPTAIOS

8

IPSABAR +

0x1A_0001

GPTA Compare Force Register

GPTACFORC

8

Table A-3. Register Memory Map (continued)

Address

Name

Mnemonic

Size

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3