3 i2c control register (i2cr), Figure 24-3, Provides a programmable pres – Motorola ColdFire MCF5281 User Manual

Page 458: C control register (i2cr), I2cr enables the i, C module and the i

I

2

C Interface

24-4

Freescale Semiconductor

24.2.3

I

2

C Control Register (I2CR)

I2CR enables the I

2

C module and the I

2

C interrupt. It also contains bits that govern operation as a slave or

a master.

IPSBAR

Offset:

0x00_0304 (I2FDR)

Access: User read/write

7

6

5

4

3

2

1

0

R

0

0

IC

W

Reset:

0

0

0

0

0

0

0

0

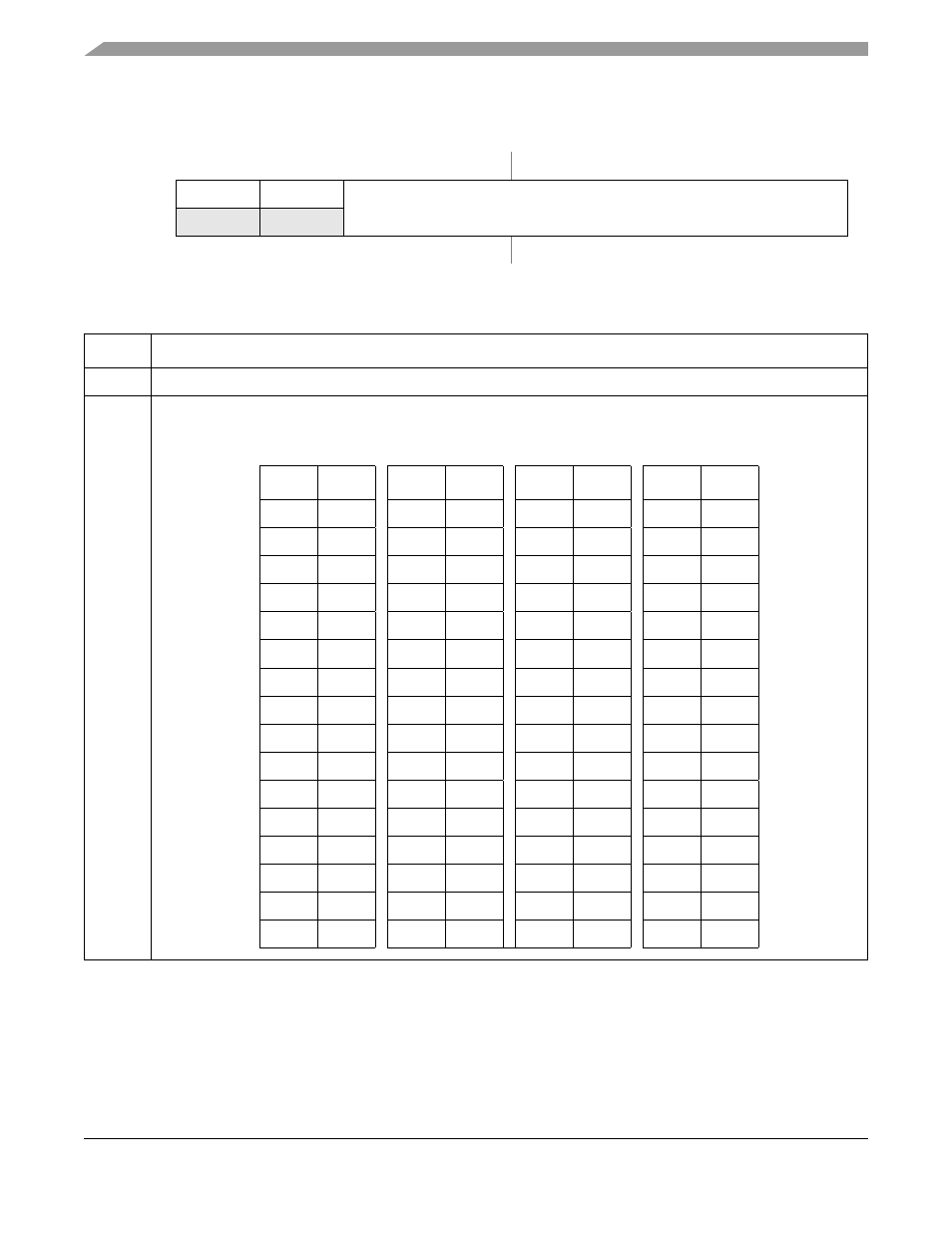

Figure 24-3. I

2

C Frequency Divider Register (I2FDR)

Table 24-3. I2FDR Field Descriptions

Field

Description

7–6

Reserved, must be cleared.

5–0

IC

I

2

C clock rate. Prescales the clock for bit-rate selection. The serial bit clock frequency is equal to the internal bus

clock divided by the divider shown below. Due to potentially slow I2C_SCL and I2C_SDA rise and fall times, bus

signals are sampled at the prescaler frequency.

IC

Divider

IC

Divider IC

Divider

IC

Divider

0x00

28

0x10

288

0x20

20

0x30

160

0x01

30

0x11

320

0x21

22

0x31

192

0x02

34

0x12

384

0x22

24

0x32

224

0x03

40

0x13

480

0x23

26

0x33

256

0x04

44

0x14

576

0x24

28

0x34

320

0x05

48

0x15

640

0x25

32

0x35

384

0x06

56

0x16

768

0x26

36

0x36

448

0x07

68

0x17

960

0x27

40

0x37

512

0x08

80

0x18

1152

0x28

48

0x38

640

0x09

88

0x19

1280

0x29

56

0x39

768

0x0A

104

0x1A

1536

0x2A

64

0x3A

896

0x0B

128

0x1B

1920

0x2B

72

0x3B

1024

0x0C

144

0x1C

2304

0x2C

80

0x3C

1280

0x0D

160

0x1D

2560

0x2D

96

0x3D

1536

0x0E

192

0x1E

3072

0x2E

112

0x3E

1792

0x0F

240

0x1F

3840

0x2F

128

0x3F

2048

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3