Motorola ColdFire MCF5281 User Manual

Page 719

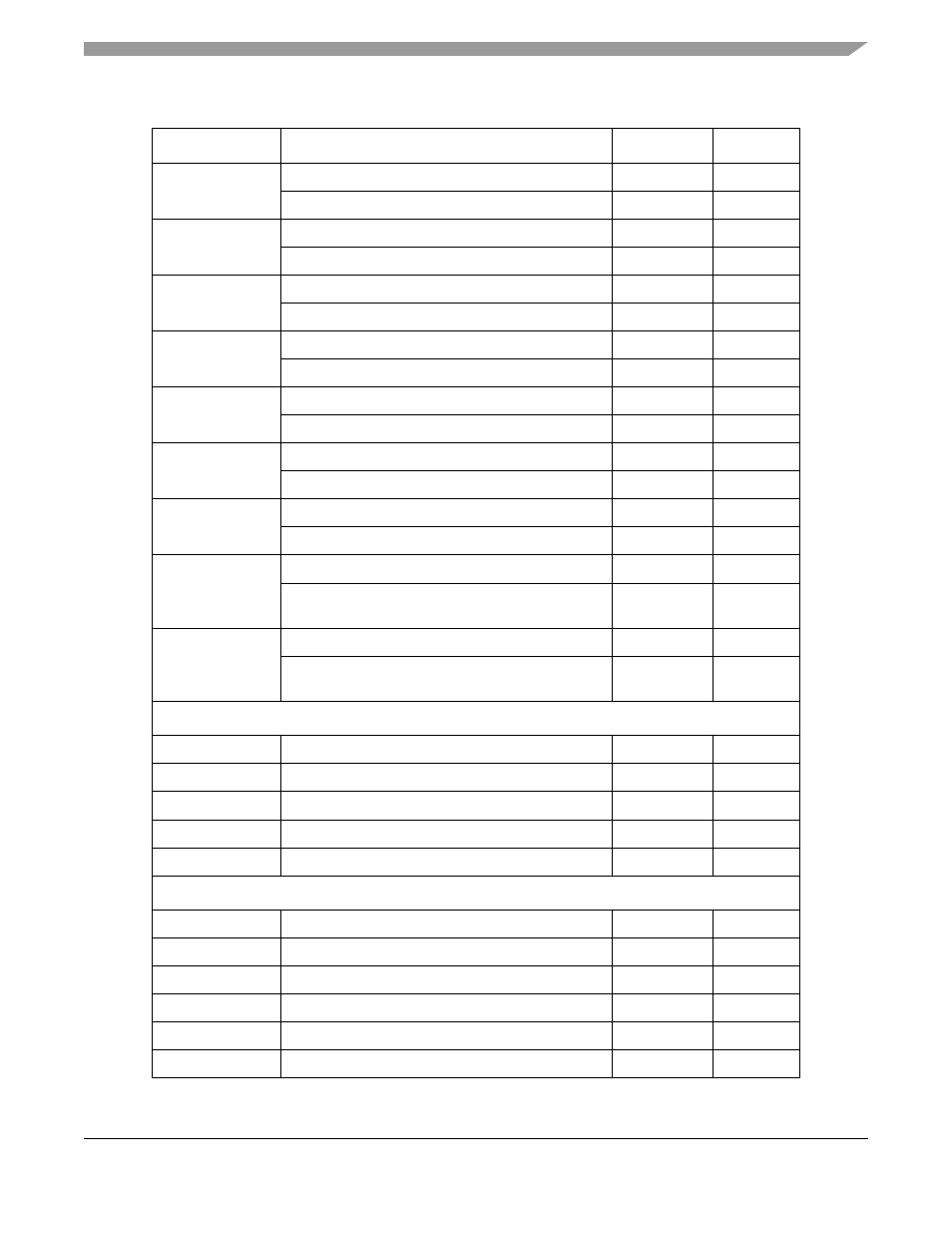

Register Memory Map

Freescale Semiconductor

A-7

IPSBAR + 0x288

(Read) Reserved

8

(Write) UART Command Register 2

UCR2

8

IPSBAR + 0x28C

(Read) UART Receive Buffer 2

URB2

8

(Write) UART Transmit Buffer 2

UTB2

8

IPSBAR + 0x290

(Read) UART Input Port Change Register 2

UIPCR2

8

(Write) UART Auxiliary Control Register 2

UACR2

8

IPSBAR + 0x294

(Read) UART Interrupt Status Register 2

UISR2

8

(Write) UART Interrupt Mask Register 2

UIMR2

8

IPSBAR + 0x298

(Read) Reserved

8

UART Baud Rate Generator Register 12

UBG12

8

IPSBAR + 0x29C

(Read) Reserved

8

UART Baud Rate Generator Register 22

UBG22

8

IPSBAR + 0x2B4

(Read) UART Input Port Register 2

UIP2

8

(Write) Reserved

8

IPSBAR + 0x2B8

(Read) Reserved

8

(Write) UART Output Port Bit Set Command Register

2

UOP12

8

IPSBAR + 0x2BC

(Read) Reserved

8

(Write) UART Output Port Bit Reset Command

Register 2

UIP02

8

I

2

C Registers

IPSBAR + 0x300

I

2

C Address Register

I2ADR

8

IPSBAR + 0x304

I

2

C Frequency Divider Register

I2FDR

8

IPSBAR + 0x308

I

2

C Control Register

I2CR

8

IPSBAR + 0x30C

I

2

C Status Register

I2SR

8

IPSBAR + 0x310

I

2

C Data I/O Register

I2DR

8

QSPI Registers

IPSBAR + 0x340

QSPI Mode Register

QMR

16

IPSBAR + 0x344

QSPI Delay Register

QDLYR

16

IPSBAR + 0x348

QSPI Wrap Register

QWR

16

IPSBAR + 0x34C

QSPI Interrupt Register

QIR

16

IPSBAR + 0x350

QSPI Address Register

QAR

16

IPSBAR + 0x354

QSPI Data Register

QDR

16

Table A-3. Register Memory Map (continued)

Address

Name

Mnemonic

Size

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3