2 address error exception, 3 illegal instruction exception – Motorola ColdFire MCF5281 User Manual

Page 65

ColdFire Core

Freescale Semiconductor

2-19

execution until all previous operations, including all pending write operations, are complete. If any

previous write terminates with an access error, it is guaranteed to be reported on the NOP instruction.

2.3.4.2

Address Error Exception

Any attempted execution transferring control to an odd instruction address (if bit 0 of the target address is

set) results in an address error exception.

Any attempted use of a word-sized index register (Xn.w) or a scale factor of eight on an indexed effective

addressing mode generates an address error, as does an attempted execution of a full-format indexed

addressing mode, which is defined by bit 8 of extension word 1 being set.

If an address error occurs on a JSR instruction, the Version 2 ColdFire processor calculates the target

address then the return address is pushed onto the stack. If an address error occurs on an RTS instruction,

the Version 2 ColdFire processor overwrites the faulting return PC with the address error stack frame.

2.3.4.3

Illegal Instruction Exception

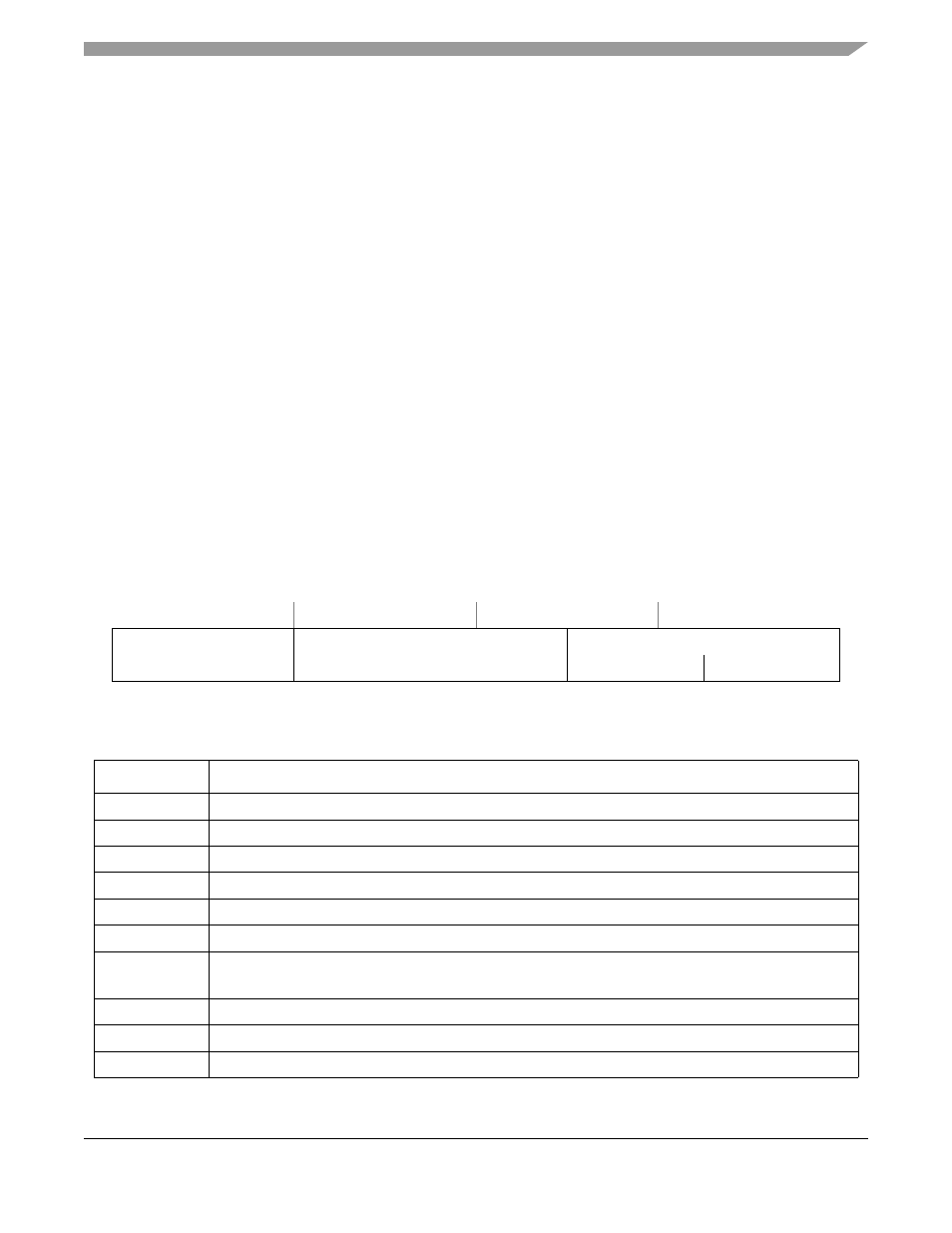

The ColdFire variable-length instruction set architecture supports three instruction sizes: 16, 32, or 48 bits.

The first instruction word is known as the operation word (or opword), while the optional words are known

as extension word 1 and extension word 2. The opword is further subdivided into three sections: the upper

four bits segment the entire ISA into 16 instruction lines, the next 6 bits define the operation mode

(opmode), and the low-order 6 bits define the effective address. See

. The opword line

.

Figure 2-17. ColdFire Instruction Operation Word (Opword) Format

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Line

OpMode

Effective Address

Mode

Register

Table 2-8. ColdFire Opword Line Definition

Opword[Line]

Instruction Class

0x0

Bit manipulation, Arithmetic and Logical Immediate

0x1

Move Byte

0x2

Move Long

0x3

Move Word

0x4

Miscellaneous

0x5

Add (ADDQ) and Subtract Quick (SUBQ), Set according to Condition Codes (Scc)

0x6

PC-relative change-of-flow instructions

Conditional (Bcc) and unconditional (BRA) branches, subroutine calls (BSR)

0x7

Move Quick (MOVEQ), Move with sign extension (MVS) and zero fill (MVZ)

0x8

Logical OR (OR)

0x9

Subtract (SUB), Subtract Extended (SUBX)

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3